# Digital Controller for Isolated Power Supply Applications

# **ADP1043A**

#### FEATURES

Integrates all typical controller functions Digital control loop Remote and local voltage sense Primary and secondary side current sense PWM control Synchronous rectifier control Current sharing Integrated programmable loop filter I<sup>2</sup>C interface Extensive fault detection and protection Extensive programming Fast calibration EEPROM Standalone or microcontroller control

#### **APPLICATIONS**

AC-to-DC power supplies Isolated dc-to-dc power supplies Redundant power supplies Parallel power supplies Server, storage, network, and communications infrastructure

#### **GENERAL DESCRIPTION**

The ADP1043A is a secondary side power supply controller IC designed to provide all the functions that are typically needed in an ac-to-dc or isolated dc-to-dc control application.

The ADP1043A is optimized for minimal component count, maximum flexibility, and minimum design time. Features include remote voltage sense, local voltage sense, primary and secondary side current sense, pulse-width modulation (PWM) generation, and hot-swap sense and control. The control loop is digital with an integrated programmable digital filter. Protection features include current limiting, ac sense, undervoltage lockout (UVLO), and overvoltage protection (OVP).

The built-in EEPROM provides extensive programming of the integrated loop filter, PWM signal timing, inrush current, and soft start timing and sequencing. Reliability is improved through a built-in checksum and redundancy of critical circuits.

A comprehensive GUI is provided for easy design of loop filter characteristics and programming of the safety features. The industry-standard  $I^2C$  bus provides access to the many monitoring and system test functions.

The ADP1043A is available in a 32-lead LFCSP and operates from a single 3.3 V supply.

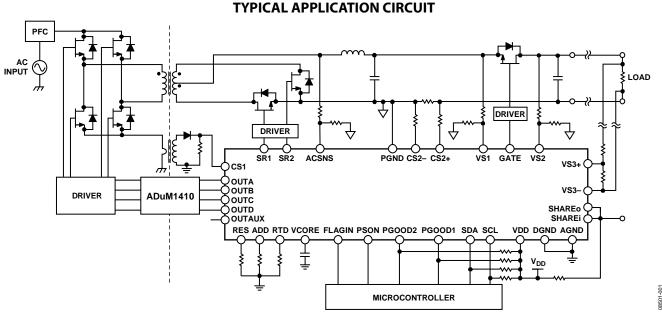

#### Figure 1.

Rev. 0 Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2009 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features 1                                                             |

|------------------------------------------------------------------------|

| Applications                                                           |

| General Description                                                    |

| Typical Application Circuit 1                                          |

| Revision History                                                       |

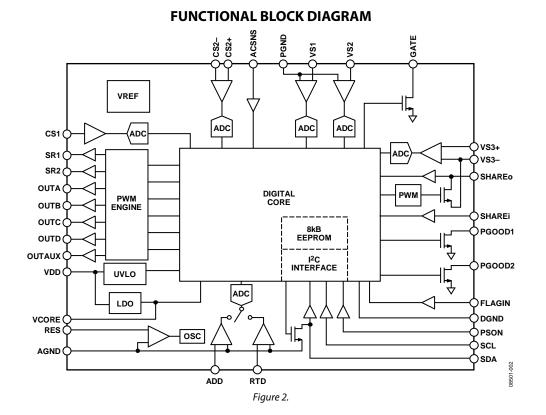

| Functional Block Diagram 4                                             |

| Specifications                                                         |

| Absolute Maximum Ratings                                               |

| Thermal Resistance                                                     |

| Soldering                                                              |

| ESD Caution                                                            |

| Pin Configuration and Function Descriptions9                           |

| Typical Performance Characteristics                                    |

| Theory of Operation12                                                  |

| Current Sense12                                                        |

| Voltage Sense and Control Loop13                                       |

| ADCs                                                                   |

| Digital Filter14                                                       |

| PWM and Sync Rect Outputs (OUTA, OUTB, OUTC, OUTD, OUTAUX, SR1, SR2)14 |

| Synchronous Rectification                                              |

| Adaptive Dead Time Control                                             |

| Light Load Mode                                                        |

| Modulation Limit                                                       |

| OrFET Control (GATE)15                                                 |

| VDD                                                                    |

| VDD/VCORE OVLO                                                         |

| Power Good18                                                           |

| Soft Start                                                             |

| Current Sharing (Share)                                                |

| Power Supply System and Fault Monitoring                               |

| Flags                                                                  |

| Monitoring Functions                                                   |

| Voltage Readings                                                       |

| Current Readings                                                       |

| Power Readings                                                         |

| Power Monitoring Accuracy                                              |

| First Flag Fault ID and Value Registers                                |

| External Flag Input (FLAGIN Pin)                                       |

| Temperature Readings (RTD Pin)                                         |

|                                                                        |

| Overtemperature Protection (OTP)               | 23 |

|------------------------------------------------|----|

| Overcurrent Protection (OCP)                   | 24 |

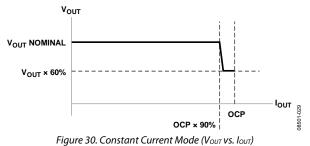

| Constant Current Mode                          | 25 |

| Overvoltage Protection (OVP)                   | 25 |

| Undervoltage Protection (UVP)                  | 25 |

| AC Sense (ACSNS)                               | 26 |

| Volt-Second Balance                            | 26 |

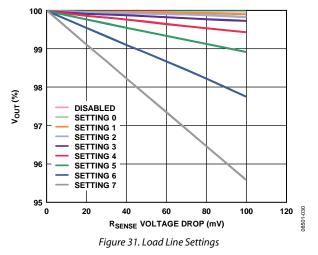

| Load Line                                      | 26 |

| Power Supply Calibration and Trim              | 27 |

| CS1 Trim                                       | 27 |

| CS2 Trim                                       | 27 |

| Voltage Calibration and Trim                   | 27 |

| Output Voltage Setting (VS3+, VS3- Trim)       | 28 |

| VS1 Trim                                       | 28 |

| VS2 Trim                                       | 28 |

| RTD/OTP Trim                                   | 28 |

| Layout Guidelines                              | 28 |

| Communication                                  | 29 |

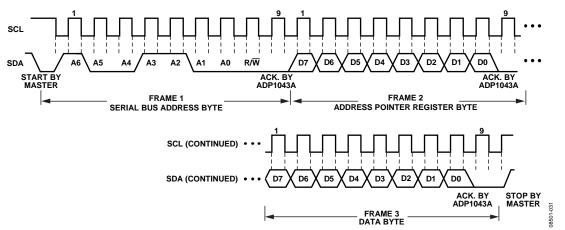

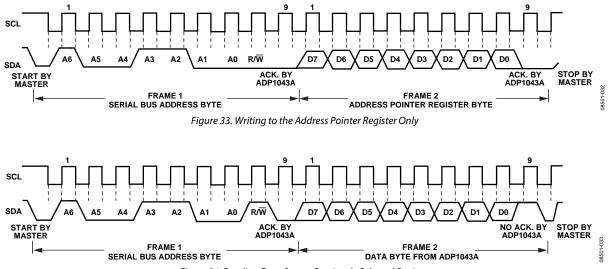

| I <sup>2</sup> C Interface                     | 29 |

| EEPROM                                         | 31 |

| Software GUI                                   | 32 |

| Register Listing                               | 33 |

| Detailed Register Descriptions                 | 35 |

| Fault Registers                                | 35 |

| Value Registers                                | 38 |

| Current Sense and Current Limit Registers      |    |

| Voltage Sense Registers                        | 46 |

| ID Registers                                   | 49 |

| PWM and Synchronous Rectifier Timing Registers | 50 |

| Digital Filter Programming Registers           | 58 |

| Adaptive Dead Time Registers                   | 60 |

| EEPROM Registers                               | 64 |

| Resonant Mode Operation                        | 65 |

| Resonant Mode Enable                           | 65 |

| PWM Timing in Resonant Mode                    | 65 |

| Synchronous Rectification in Resonant Mode     | 65 |

| Adjusting the Timing of the PWM Outputs        | 66 |

| Frequency Limit Setting                        | 66 |

| Feedback Control in Resonant Mode              | 66 |

| Soft Start in Resonant Mode                    | 66 |

| Light Load Operation (Burst Mode)60 | 5 |

|-------------------------------------|---|

| OUTAUX in Resonant Mode60           | 6 |

| Protections in Resonant Mode66      | 6 |

| Resonant Mode Register Descriptions67 |

|---------------------------------------|

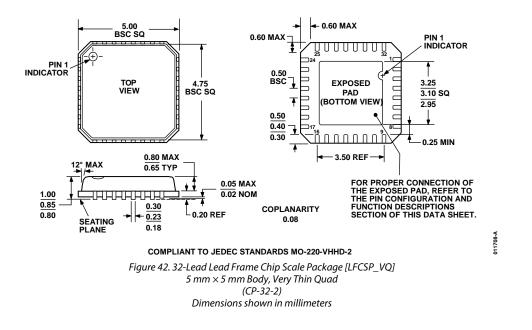

| Outline Dimensions71                  |

| Ordering Guide71                      |

# **REVISION HISTORY**

10/09—Revision 0: Initial Version

The ADP1043A is a secondary side controller for switch mode power supplies (SMPS). It is designed for use in isolated redundant applications. The ADP1043A integrates the typical functions that are needed to control a power supply. These include

- Output voltage sense and feedback

- Digital loop filter compensation

- PWM generation

- Current sharing

- Current, voltage, and temperature sense

- OrFET control

- Housekeeping and I<sup>2</sup>C interface

- Calibration and trimming

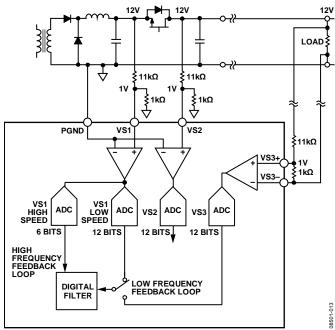

The main function of controlling the output voltage is performed using the feedback ADCs, the digital loop filter, and the PWM block. The feedback ADCs use a multipath approach (patent pending). The ADP1043A combines a high speed, low resolution (fast and coarse) ADC and a low speed, high resolution (slow and accurate) ADC. Loop compensation is implemented using the digital filter. This PID (proportional, integral, derivative) filter is implemented in the digital domain to allow easy programming of filter characteristics, which is of great value in customizing and debugging designs.

The PWM block generates up to seven programmable PWM outputs for control of FET drivers and synchronous rectification FET drivers. This programmability allows many traditional and unique switching topologies to be realized. A current share bus interface provides for parallel power supplies. The part also has hot-swap OrFET sense and control for N + 1 redundant power supplies.

Conventional power supply housekeeping features, such as remote and local voltage sense and primary and secondary side current sense, are included. An extensive set of protections is offered, including overvoltage protection (OVP), overcurrent protection (OCP), overtemperature protection (OTP), undervoltage protection (UVP), ground continuity monitoring, and ac sense.

All these features are programmable through the I<sup>2</sup>C bus interface. This bus interface is also used to calibrate the power supply. Other information, such as input current, output current, and fault flags, is also available through the I<sup>2</sup>C bus interface.

The internal EEPROM can store all programmed values and allows standalone control without a microcontroller. A free, downloadable GUI is available that provides all the necessary software to program the ADP1043A. For more information about the GUI, contact Analog Devices, Inc., for the latest software and a user guide.

The ADP1043A operates from a single 3.3 V supply and is specified from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

# **SPECIFICATIONS**

$V_{DD}$  = 3.3 V,  $T_A$  = -40°C to +85°C, unless otherwise noted. FSR = full-scale range.

#### Table 1.

| Parameter                                        | Symbol          | Test Conditions/Comments                                          | Min                   | Тур          | Max    | Unit  |

|--------------------------------------------------|-----------------|-------------------------------------------------------------------|-----------------------|--------------|--------|-------|

| SUPPLY                                           |                 |                                                                   |                       |              |        |       |

| V <sub>DD</sub>                                  | V <sub>DD</sub> |                                                                   | 3.1                   | 3.3          | 3.6    | V     |

| IDD                                              | IDD             | Normal operation (PSON is high)                                   |                       | 20           |        | mA    |

|                                                  |                 | Power supply off (PSON is low)                                    |                       | 15           |        | mA    |

|                                                  |                 | During EEPROM programming (40 ms)                                 |                       | $I_{DD} + 8$ |        | mA    |

| POWER-ON RESET                                   |                 |                                                                   |                       |              |        |       |

| Power-On Reset                                   |                 | V <sub>DD</sub> rising                                            | 3.05                  |              |        | V     |

| UVLO                                             |                 | V <sub>DD</sub> falling                                           | 2.75                  | 2.85         | 2.95   | V     |

| UVLO Hysteresis                                  |                 |                                                                   |                       | 35           |        | mV    |

| OVLO                                             |                 |                                                                   | 3.7                   | 3.9          | 4.1    | V     |

| VCORE PIN                                        |                 |                                                                   |                       |              |        |       |

| Output Voltage                                   |                 | $T_A = 25^{\circ}C$                                               | 2.3                   | 2.5          | 2.7    | V     |

| OSCILLATOR AND PLL                               |                 |                                                                   |                       |              |        |       |

| PLL Frequency                                    |                 | $RES = 49.9 k\Omega$                                              | 190                   | 200          | 210    | MHz   |

| OUTA, OUTB, OUTC, OUTD,<br>OUTAUX, SR1, SR2 PINS |                 |                                                                   |                       |              |        |       |

| Output Low Voltage                               | Vol             | Source current = 10 mA                                            |                       |              | 0.4    | V     |

| Output High Voltage                              | Vон             | Source current = 10 mA                                            | $V_{\text{DD}} - 0.4$ |              |        | v     |

| Rise Time                                        |                 | $C_{LOAD} = 50 \text{ pF}$                                        |                       | 3.5          |        | ns    |

| Fall Time                                        |                 | $C_{LOAD} = 50 \text{ pF}$                                        |                       | 1.5          |        | ns    |

| AC SENSE                                         |                 | PWM and resonant mode                                             |                       |              |        |       |

| Input Voltage Threshold                          |                 |                                                                   | 0.3                   | 0.45         | 0.65   | V     |

| Propagation Delay                                |                 | From ACSNS threshold to SR start;<br>resonant mode only           |                       | 160          |        | ns    |

| VS1, VS2, VS3 LOW SPEED ADC                      |                 |                                                                   |                       |              |        |       |

| Input Voltage Range                              | VIN             | Differential voltage from VS1, VS2 to PGND, and from VS3+ to VS3– | 0                     | 1            | 1.55   | V     |

| Sampling Frequency                               | <b>f</b> samp   |                                                                   |                       | 100          |        | Hz    |

| Voltage Sense Measurement<br>Accuracy            |                 | From 0% to 100% of input voltage range                            | -10                   |              | +10    | % FSR |

|                                                  |                 |                                                                   | -155                  |              | +155   | mV    |

|                                                  |                 | From 10% to 90% of input voltage range                            | -2.5                  |              | +2.5   | % FSR |

|                                                  |                 |                                                                   | -38.75                |              | +38.75 | mV    |

|                                                  |                 | From 900 mV to 1.1 V                                              | -1.5                  |              | +1.5   | % FSR |

|                                                  |                 |                                                                   | -23.25                |              | +23.25 | mV    |

| Voltage Sense Measurement<br>Resolution          |                 |                                                                   |                       | 12           |        | Bits  |

| Voltage Differential from VS3–<br>to PGND        |                 |                                                                   | -200                  |              | +200   | mV    |

| VS1 OVP Comparator Speed                         |                 | Register $0x2C[2] = 0$                                            |                       | 300          |        | μs    |

| VS1 OVP Threshold Accuracy                       |                 | Relative to nominal voltage (1 V) on VS1                          |                       | 2.5          |        | %     |

| VS2 and VS3 OVP Comparator<br>Speed              |                 | Register 0x2C[2] = 0                                              |                       | 300          |        | μs    |

| VS2 and VS3 OVP Threshold<br>Accuracy            |                 | Relative to nominal voltage (1 V) on VS2<br>and VS3               |                       | 2.5          |        | %     |

| VS1 HIGH SPEED ADC                               |                 |                                                                   |                       |              |        |       |

| Sampling Frequency                               | <b>f</b> samp   |                                                                   |                       | 400          |        | kHz   |

| Resolution                                       |                 |                                                                   |                       | 6            |        | Bits  |

| Dynamic Range                                    |                 |                                                                   |                       | ±18          |        | mV    |

| Parameter                               | Symbol          | Test Conditions/Comments               | Min   | Тур         | Max        | Unit  |

|-----------------------------------------|-----------------|----------------------------------------|-------|-------------|------------|-------|

| CURRENT SENSE 1 (CS1 PIN)               |                 |                                        |       |             |            |       |

| Input Voltage Range                     | VIN             |                                        | 0     | 1           | 1.38       | V     |

| Sampling Frequency                      | <b>f</b> samp   |                                        |       | 100         |            | Hz    |

| Current Sense Measurement<br>Accuracy   |                 | From 10% to 90% of input voltage range | -3.0  |             | +3.0       | % FSR |

|                                         |                 |                                        | -41.4 |             | +41.4      | mV    |

|                                         |                 | From 0% to 100% of input voltage range | -10   |             | +10        | % FSR |

|                                         |                 |                                        | -138  |             | +138       | mV    |

| Current Sense Measurement<br>Resolution |                 |                                        |       | 12          |            | Bits  |

| CS1 Fast OCP Threshold                  |                 |                                        | 1.1   | 1.2         | 1.3        | v     |

| CS1 Fast OCP Speed                      |                 |                                        |       | 80          | 100        | ns    |

| CS1 Accurate OCP DC Accuracy            |                 | From 10% to 90% of input voltage range | -3.0  |             | +3.0       | % FSR |

| ,                                       |                 |                                        | -41.4 |             | +41.4      | mV    |

| CS1 Accurate OCP Speed                  |                 |                                        |       | 10          |            | ms    |

| Leakage Current                         |                 |                                        |       | 4.0         |            | μA    |

| CURRENT SENSE 2 (CS2+, CS2–             |                 |                                        | 1     |             |            | 1     |

| PINS)                                   |                 |                                        |       |             |            |       |

| Input Voltage Range                     | VIN             | Differential voltage from CS2+ to CS2– | -100  |             | +225       | mV    |

| ADC Input Voltage Range                 |                 | LSB = 61.04 μV                         | 0     |             | 225        | mV    |

| Sampling Frequency                      | <b>f</b> samp   |                                        |       | 100         |            | Hz    |

| Current Sense Measurement<br>Accuracy   |                 | From 0 mV to 200 mV                    | -4    |             | +4         | mV    |

|                                         |                 | From 200 mV to 225 mV                  | -15   |             | +15        | mV    |

|                                         |                 |                                        | -7.5  |             | +7.5       | % FSR |

| Current Sense Measurement<br>Resolution |                 |                                        |       | 12          |            | Bits  |

| CS2 Accurate OCP Accuracy               |                 | From 0 mV to 200 mV                    | -4    |             | +4         | mV    |

| ,                                       |                 | From 200 mV to 225 mV                  | -15   |             | +15        | mV    |

|                                         |                 |                                        | -7.5  |             | +7.5       | % FSR |

| CS2 Accurate OCP Speed                  |                 |                                        |       | 10          |            | ms    |

| Current Sink (High Side)                |                 |                                        |       | 100         |            | μΑ    |

| Current Source (Low Side)               |                 |                                        |       | 100         |            | μA    |

| Common-Mode Voltage at the              |                 | To achieve CS2 measurement accuracy    | 0.8   | 100         | 1.3        | V     |

| CS2+ and CS2– Pins                      |                 | To demote est medsarement decardey     | 0.0   |             | 1.5        | •     |

| GATE PIN (OPEN DRAIN)                   |                 |                                        |       |             |            |       |

| Output Low Voltage                      | V <sub>OL</sub> |                                        |       |             | 0.4        | v     |

| DrFET PROTECTION (CS2+, CS2–)           |                 | Low-side current sensing only          |       |             |            |       |

| Accurate OrFET Threshold<br>Accuracy    |                 |                                        | -1.2  | 0           | +1         | mV    |

| Accurate OrFET Speed                    |                 |                                        |       | 10          |            | ms    |

| Fast OrFET Accuracy                     |                 | –25 mV setting                         | -40   | -25         | -10        | mV    |

| rast on ET Accuracy                     |                 | -50 mV setting                         | -40   | -25<br>-50  | -10<br>-30 | mV    |

|                                         |                 | –75 mV setting                         | -100  |             | -30<br>-50 | mV    |

|                                         |                 | -100 mV setting                        | -100  | -75<br>-100 |            | mV    |

| East OrEET Spood                        |                 | Debounce = $40 \text{ ns}$             | -125  |             |            |       |

| Fast OrFET Speed                        |                 |                                        |       | 110         | 150        | ns    |

| RTD PIN                                 | V               |                                        |       | 1           | 1 55       | V     |

| Input Voltage Range                     | VIN             | PTD register = 100 kO                  | 0     | 1           | 1.55       | V     |

| Current Source                          |                 | RTD resistor = $100 \text{ k}\Omega$   | 9.5   | 10.8        | 12         | μΑ    |

| RTD ADC Measurement<br>Accuracy         |                 | From 2% to 20% of input voltage range  | -1    |             | +1         | % FSR |

| •                                       |                 | From 32 mV to 320 mV                   | -15.5 |             | +15.5      | mV    |

|                                         |                 | From 0% to 100% of input voltage range | -10   |             | +10        | % FSR |

|                                         | 1               | From 0 V to 1.55 V                     | -155  |             | +155       | mV    |

| Parameter                                     | Symbol              | Test Conditions/Comments  | Min                   | Тур | Max   | Unit   |

|-----------------------------------------------|---------------------|---------------------------|-----------------------|-----|-------|--------|

| OTP Threshold Accuracy                        |                     | When RTD = 10 k $\Omega$  | -0.5                  |     | +0.5  | % FSR  |

|                                               |                     |                           | -7.75                 |     | +7.75 | mV     |

|                                               |                     | When RTD = 100 k $\Omega$ | -5                    |     | +5    | % FSR  |

|                                               |                     |                           | -77.5                 |     | +77.5 | mV     |

| OTP Speed                                     |                     |                           |                       | 10  |       | ms     |

| OTP Threshold Hysteresis                      |                     | When RTD = 10 k $\Omega$  |                       | 16  |       | mV     |

| PGOOD1, PGOOD2, SHAREO PINS<br>(OPEN DRAIN)   |                     |                           |                       |     |       |        |

| Output Low Voltage                            | V <sub>OL</sub>     |                           |                       |     | 0.4   | V      |

| PSON, FLAGIN, SHAREI PINS<br>(DIGITAL INPUTS) |                     |                           |                       |     |       |        |

| Input Low Voltage                             | VIL                 |                           |                       |     | 0.4   | V      |

| Input High Voltage                            | VIH                 |                           | $V_{\text{DD}} - 0.8$ |     |       | V      |

| SDA/SCL PINS                                  |                     | $V_{DD} = 3.3 \text{ V}$  |                       |     |       |        |

| Input Low Voltage                             | VIL                 |                           |                       |     | 0.4   | V      |

| Input High Voltage VIH                        |                     |                           | $V_{\text{DD}} - 0.8$ |     |       | V      |

| Output Low Voltage Vol                        |                     |                           |                       |     | 0.4   | V      |

| Leakage Current                               |                     |                           | -5                    |     | +5    | μΑ     |

| SERIAL BUS TIMING                             |                     |                           |                       |     |       |        |

| Clock Frequency                               |                     |                           |                       | 100 | 400   | kHz    |

| Glitch Immunity                               | tsw                 |                           |                       |     | 50    | ns     |

| Bus-Free Time                                 | t <sub>BUF</sub>    |                           | 4.7                   |     |       | μs     |

| Start Setup Time                              | tsu;sta             |                           | 4.7                   |     |       | μs     |

| Start Hold Time                               | thd;sta             |                           | 4                     |     |       | μs     |

| SCL Low Time                                  | t <sub>LOW</sub>    |                           | 4.7                   |     |       | μs     |

| SCL High Time                                 | thigh               |                           | 4                     |     |       | μs     |

| SCL, SDA Rise Time                            | t <sub>R</sub>      |                           |                       |     | 1000  | ns     |

| SCL, SDA Fall Time                            | tF                  |                           |                       |     | 300   | ns     |

| Data Setup Time                               | t <sub>su;dat</sub> |                           | 250                   |     |       | ns     |

| Data Hold Time                                | thd;dat             |                           | 300                   |     |       | ns     |

| EEPROM RELIABILITY                            |                     |                           |                       |     |       |        |

| Endurance <sup>1</sup>                        |                     |                           | 10,000                |     |       | Cycles |

| Data Retention <sup>2</sup>                   |                     | T_ = 85°C                 | 20                    |     |       | Years  |

<sup>1</sup> Endurance is qualified as per JEDEC Standard 22, Method A117, and is measured at -40°C, +25°C, +85°C, and +125°C. <sup>2</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 85°C as per JEDEC Standard 22, Method A117. Retention lifetime derates with junction temperature.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                          | Rating                            |

|------------------------------------|-----------------------------------|

| Supply Voltage (Continuous) VDD    | 4.2 V                             |

| Digital Pins                       | -0.3 V to V <sub>DD</sub> + 0.3 V |

| VS3– to PGND, AGND, DGND           | –0.3 V to +0.3 V                  |

| RTD, VS1 to AGND                   | 2.5 V                             |

| VS2, VS3+, ADD to AGND             | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Operating Temperature Range        | -40°C to +85°C                    |

| Storage Temperature Range          | -65°C to +150°C                   |

| Junction Temperature               | 150°C                             |

| Peak Solder Reflow Temperature     |                                   |

| SnPb Assemblies (10 sec to 30 sec) | 240°C                             |

| RoHS-Compliant Assemblies          | 260°C                             |

| (20 sec to 40 sec)                 |                                   |

| ESD Charged Device Model           | 1.5 kV                            |

| ESD Human Body Model               | 3.5 kV                            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type  | θ <sub>JA</sub> | οlo | Unit |

|---------------|-----------------|-----|------|

| 32-Lead LFCSP | 44.4            | 6.4 | °C/W |

### SOLDERING

It is important to follow the correct guidelines when laying out the PCB footprint for the ADP1043A and when soldering the part onto the PCB. The AN-772 Application Note discusses this topic in detail (see www.analog.com).

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

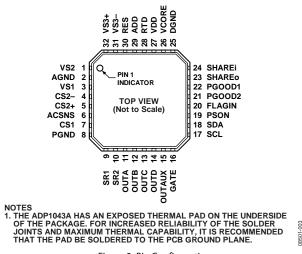

Figure 3. Pin Configuration

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VS2      | Power Supply Output Sense Input. This signal is referred to PGND. Input to a low frequency $\Sigma$ - $\Delta$ ADC. Nominal voltage at this pin should be 1 V. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming.                                                                                                                                                                                                                                          |

| 2       | AGND     | Analog Ground. This pin is the ground for the analog circuitry of the ADP1043A. Star connect to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3       | VS1      | Local Voltage Sense Input. This signal is referred to PGND. Input to a high frequency $\Sigma$ - $\Delta$ ADC. Nominal voltage at this pin should be 1 V. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming.                                                                                                                                                                                                                                               |

| 4       | CS2–     | Inverting Differential Current Sense Input. Nominal voltage at this pin should be 1 V for best operation. When using high-side current sensing in a 12 V application, place a 110 k $\Omega$ resistor between the sense resistor and this pin. When using low-side current sensing, place a 10 k $\Omega$ resistor between the sense resistor and this pin. When using high-side current sensing, use the formula R = (V <sub>COMMONMODE</sub> – 1)/100 µA. A 0.1% resistor must be used to connect this circuit.       |

| 5       | CS2+     | Noninverting Differential Current Sense Input. Nominal voltage at this pin should be 1 V for best operation.<br>When using high-side current sensing in a 12 V application, place a 110 k $\Omega$ resistor between the sense resistor and this pin. When using low-side current sensing, place a 10 k $\Omega$ resistor between the sense resistor and this pin. When using high-side current sensing, use the formula R = (V <sub>COMMONMODE</sub> – 1)/100 µA. A 0.1% resistor must be used to connect this circuit. |

| 6       | ACSNS    | AC Sense Input. This input is connected upstream of the main inductor through a resistor divider network.<br>The nominal voltage for this circuit is 0.45 V. This signal is referred to PGND.                                                                                                                                                                                                                                                                                                                           |

| 7       | CS1      | Primary Side Current Sense Input. This pin is the current transformer input to measure and control the primary side current. This signal is referred to PGND. The resistors on this input must have a tolerance specification of 0.5% or better to allow for trimming.                                                                                                                                                                                                                                                  |

| 8       | PGND     | Power Ground. This pin is the ground connection for the main power rail of the power supply. Star connect to AGND.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9       | SR1      | Synchronous Rectifier Output. This PWM output connects to the input of a FET driver. This pin can be disabled when not in use. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                         |

| 10      | SR2      | Synchronous Rectifier Output. This PWM output connects to the input of a FET driver. This pin can be disabled when not in use. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                         |

| 11      | OUTA     | PWM Output for Primary Side Switch. This pin can be disabled when not in use. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12      | OUTB     | PWM Output for Primary Side Switch. This pin can be disabled when not in use. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13      | OUTC     | PWM Output for Primary Side Switch. This pin can be disabled when not in use. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14      | OUTD     | PWM Output for Primary Side Switch. This pin can be disabled when not in use. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15      | OUTAUX   | Auxiliary PWM Output. This pin can be disabled when not in use. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16      | GATE     | OrFET Gate Drive Output (Open Drain). This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 17      | SCL      | I <sup>2</sup> C Serial Clock Input. This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18      | SDA      | I <sup>2</sup> C Serial Data Input and Output (Open Drain). This signal is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin No.        | Mnemonic | Description                                                                                                                                                                                                                                                        |

|----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19             | PSON     | Power Supply On Input. This signal is referred to DGND. This is the hardware PSON control signal. It is recommended that a 1 nF capacitor be included from the PSON pin to DGND for noise debounce and decoupling.                                                 |

| 20             | FLAGIN   | Flag Input. An external signal can be input at this pin to generate a flag condition.                                                                                                                                                                              |

| 21             | PGOOD2   | Power-Good Output (Open Drain). This signal is referred to AGND. This pin is controlled by the PGOOD2 flag. This pin is set if any flag is set.                                                                                                                    |

| 22             | PGOOD1   | Power-Good Output (Open Drain). This signal is referred to AGND. This pin is controlled by the PGOOD1 flag. This pin is set if any of the following are out of range: power supply, CS1 fast OCP, CS1 accurate OCP, CS2 accurate OCP, UVP, local OVP, or load OVP. |

| 23             | SHAREo   | Share Bus Output Voltage Pin. Connect this pin to 3.3 V through a 2.2 kΩ resistor. When configured as a digital share bus, this pin is a digital output. This signal is referred to AGND.                                                                          |

| 24             | SHAREi   | Share Bus Feedback Pin. Connect this pin to the SHAREo pin. This signal is referred to AGND.                                                                                                                                                                       |

| 25             | DGND     | Digital Ground. This pin is the ground for the digital circuitry of the ADP1043A. Star connect to AGND.                                                                                                                                                            |

| 26             | VCORE    | Output of 2.5 V Regulator. Connect a 100 nF capacitor from this pin to DGND.                                                                                                                                                                                       |

| 27             | VDD      | Positive Supply Input. Range is from 3.1 V to 3.6 V. This signal is referred to AGND.                                                                                                                                                                              |

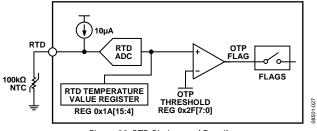

| 28             | RTD      | Thermistor Input. A 100 k $\Omega$ thermistor is placed from this pin to AGND. This signal is referred to AGND.                                                                                                                                                    |

| 29             | ADD      | Address Select Input. Connect a resistor from ADD to AGND. This signal is referred to AGND.                                                                                                                                                                        |

| 30             | RES      | Resistor Input. This pin sets up the internal voltage reference for the ADP1043A. Connect a 49.9 k $\Omega$ resistor (±0.1%) from RES to AGND. This signal is referred to AGND.                                                                                    |

| 31             | VS3–     | Inverting Remote Voltage Sense Input. There should be a low ohmic connection to AGND. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming.                                                              |

| 32             | VS3+     | Noninverting Remote Voltage Sense Input. This signal is referred to VS3–. Use 0.1% resistors as the resistor divider to connect this circuit. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming.      |

| Exposed<br>Pad | EP       | The ADP1043A has an exposed thermal pad on the underside of the package. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the pad be soldered to the PCB ground plane.                                        |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

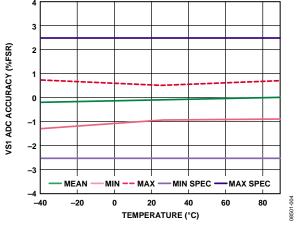

Figure 4. VS1 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

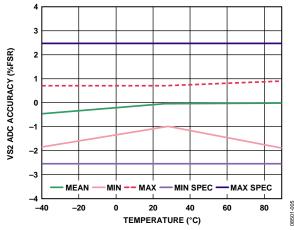

Figure 5. VS2 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

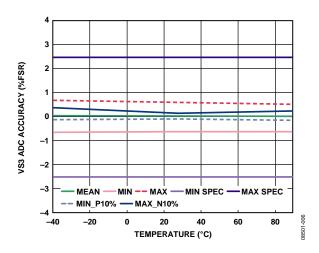

Figure 6. VS3 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

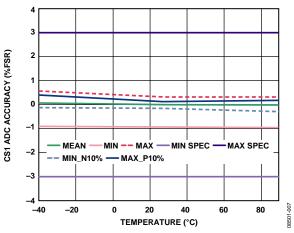

Figure 7. CS1 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

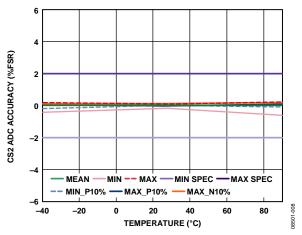

Figure 8. CS2 ADC Accuracy vs. Temperature (from 0 mV to 200 mV)

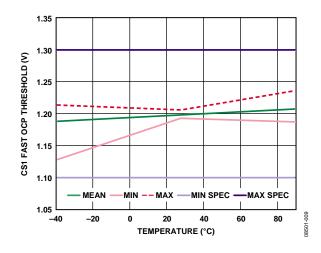

Figure 9. CS1 Fast OCP Threshold vs. Temperature

# **THEORY OF OPERATION**

# **CURRENT SENSE**

The ADP1043A has two individual current sense inputs: CS1 and CS2±. These inputs sense, protect, and control the output current and the share bus information. They can be calibrated to remove any errors due to external components.

### CS1 Operation (CS1)

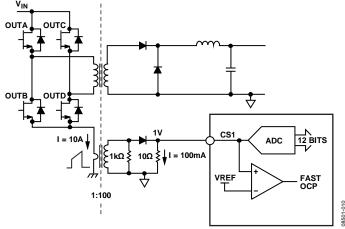

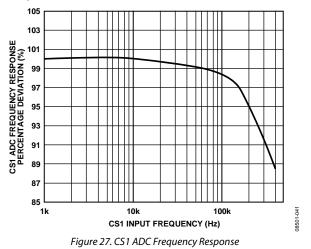

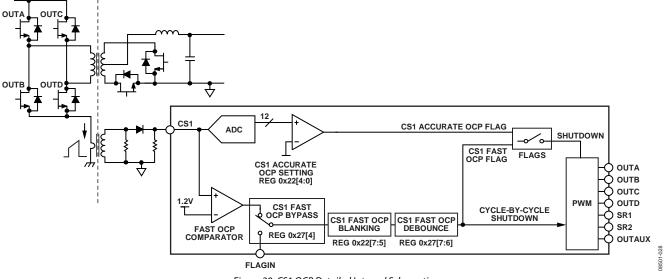

CS1 is typically used for the monitoring and protection of the primary side current. This is commonly known as the current transformer (CT) method of current sensing. The input signal at the CS1 pin is fed into an ADC for current monitoring. The range of the ADC is 0 V to 1.38 V. The input signal is also fed into a comparator for fast OCP protection. The typical configuration for the current sense is shown in Figure 10.

Figure 10. Current Sense 1 (CS1) Operation

The comparator effectively measures peak current, and the ADC effectively measures the average current information. This information is available through the I<sup>2</sup>C interface. Various thresholds and limits can be set for CS1, such as OCP. These thresholds and limits are described in the Current Sense and Current Limit Registers section.

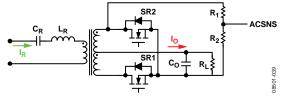

# CS2 Operation (CS2+, CS2-)

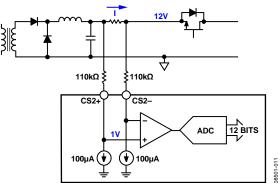

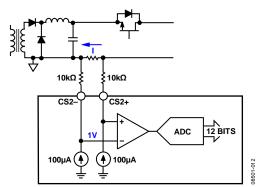

CS2± is used for the monitoring and protection of the secondary side current. The full-scale range of the CS2 ADC is 225 mV. The nominal full load voltage drop can be configured for 37.5 mV, 75 mV, or 150 mV. The differential inputs are fed into an ADC through a pair of external resistors. When using low-side current sensing, a 10 k $\Omega$  resistor is required. When using high-side current sensing, a 110 k $\Omega$  resistor is required (for a 12 V application).

Low-side current sensing is recommended because it provides improved performance compared with high-side current sensing. High-side current sensing is not supported for applications where the output voltage is above 20 V common mode. (There is not enough offset trim range above 20 V common mode.)

Typical configurations are shown in Figure 11 and Figure 12. Various thresholds and limits can be set for CS2, such as OCP. These thresholds and limits are described in the Current Sense and Current Limit Registers section.

When not in use, both CS2 inputs should be connected through 10  $k\Omega$  resistors to PGND.

Figure 11. High-Side Resistive Current Sense

Figure 12. Low-Side Resistive Current Sense (Recommended)

### **VOLTAGE SENSE AND CONTROL LOOP**

Multiple voltage sense inputs on the ADP1043A are used for the monitoring, control, and protection of the power supply output. The voltage information is available through the I<sup>2</sup>C interface. All voltage sense points can be calibrated digitally to remove any errors due to external components. This calibration can be performed in the production environment, and the settings can be stored in the EEPROM of the ADP1043A (see the Power Supply Calibration and Trim section for more information).

The update rate of the ADC from a control loop standpoint is set to the switching frequency. Therefore, if the switching frequency is set to 100 kHz, the ADC outputs a signal every 100 kHz to the control loop. Because the  $\Sigma$ - $\Delta$  modulators of the ADC sample at 1.6 MHz, the output of the ADC is the average of the 16 readings taken during the 1.6 MHz time frame.

For voltage monitoring, the VS1, VS2, and VS3 voltage value registers are updated every 10 ms. The ADP1043A stores every ADC sample for 10 ms and then outputs the average value at the end of the 10 ms period. Therefore, if these registers are read at least every 10 ms, a true average value is read. The same applies to the CS1 and CS2 current readings.

For the control loop, the high speed signal always comes from the VS1 high speed ADC. The low speed signal normally comes from the VS3 low speed ADC. However, during soft start or in response to a load OVP or other fault condition, the ADP1043A can switch its low speed regulating point from VS3 to VS1.

Figure 13. Voltage Sense Configuration

#### VS1 Operation (VS1)

VS1 is used for the monitoring and protection of the power supply voltage at the output of the LC stage, upstream of the OrFET. This is also the high frequency feedback loop for the power supply. The VS1 sense point on the power rail needs an external resistor divider to bring the nominal common-mode signal to 1 V at the VS1 pin (see Figure 13). The resistor divider is necessary because the ADP1043A VS1 ADC input range is 0 V to 1.55 V. This divided-down signal is internally fed into a high speed and a low speed  $\Sigma$ - $\Delta$  ADC. The output of the VS1 ADC sgoes to the digital filter.

The high speed ADC has a 2 MHz bandwidth and is run from a 25 MHz clock. It has a range of  $\pm 18$  mV. When the sampling rate is 200 kHz, there is 0.6 mV (two LSBs) of quantization noise. Increasing the sampling rate to 400 kHz increases the quantization noise to 1.2 mV.

In the event of a load overvoltage condition, the power supply is regulated from the VS1 sense point, rather than from the VS3 sense point.

#### VS2 Operation (VS2)

VS2 is typically used for the monitoring and protection of the output of the power supply, downstream of the OrFET. It is used with VS1 to control the OrFET gate drive turn-on. The VS2 sense point on the power rail needs an external resistor divider to bring the nominal common-mode signal to 1 V at the VS2 pin (see Figure 13). The resistor divider is necessary because the ADP1043A VS2 ADC input range is 0 V to 1.55 V. This divided-down signal is internally fed into an ADC. The output of the VS2 ADC goes to the VS2 voltage value register (Register 0x16).

#### VS3 Operation (VS3+, VS3-)

VS3± is used for the monitoring and protection of the remote load voltage. It is a fully differential input. This is the main feedback sense point for the power supply control loop. The VS3 sense point on the power rail needs an external resistor divider to bring the nominal common-mode signal to 1 V at the VS3± pins (see Figure 13). The resistor divider is necessary because the ADP1043A VS3 ADC input range is 0 V to 1.55 V. This divided-down signal is internally fed into an ADC. The output of the VS3 ADC goes to the digital filter.

#### ADCs

The ADP1043A includes several ADCs. The high speed ADC is described in the VS1 Operation (VS1) section. The other ADCs are low speed, high resolution. They have a 1 kHz bandwidth and 12-bit resolution. Each ADC has its own voltage reference for added protection from potential failure. The digital output of each ADC is readable through the appropriate value register.

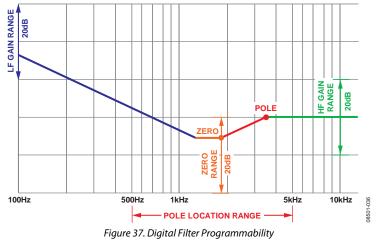

### **DIGITAL FILTER**

The loop response of the power supply can be changed using the internal programmable digital filter. A Type 3 filter architecture has been implemented. To tailor the loop response to the specific application, the low frequency gain, zero location, pole location, and high frequency gain can all be set individually (see the Digital Filter Programming Registers section). It is recommended that the Analog Devices software GUI be used to program the filter. The software GUI displays the filter response in Bode plot format and can be used to calculate all stability criteria for the power supply.

From the sensed voltage to the duty cycle, the transfer function of the filter in z-domain is as follows:

$$H(z) = \left(\frac{d}{202.24 \times m} \times \frac{z}{z-1}\right) + \left(\frac{c}{7.68} \times \frac{z-b}{z-a}\right)$$

(1)

where:

$a = \text{filter_pole_register_value/256.}$   $b = \text{filter_zero_register_value/256.}$   $c = \text{high_frequency_gain_register_value.}$   $m = 1 \text{ when } 48.8 \text{ kHz} \le f_{\text{SW}} < 97.7 \text{ kHz.}$   $m = 2 \text{ when } 97.7 \text{ kHz} \le f_{\text{SW}} < 195.3 \text{ kHz.}$   $m = 4 \text{ when } 195.3 \text{ kHz} \le f_{\text{SW}} < 390.6 \text{ kHz.}$  $m = 8 \text{ when } 390.6 \text{ kHz} \le f_{\text{SW}}.$

To go from z-domain to s-domain, plug the following equation into the H(z) equation:

$$z(s) = \frac{2f_{SW} + s}{2f_{SW} - s}$$

where *f<sub>sw</sub>* is the switching frequency.

The digital filter introduces an extra phase delay element into the control loop. The digital filter circuit sends the duty cycle information to the PWM circuit at the beginning of each switching cycle (unlike an analog controller, which makes decisions on the duty cycle information continuously). Therefore, the extra phase delay for phase margin,  $\Phi$ , introduced by the filter block is

$\Phi = 180 \times (f_C/f_{SW})$

where:

$f_C$  is the crossover frequency.  $f_{SW}$  is the switching frequency.

At one tenth of the switching frequency, the phase delay is 18°. The GUI incorporates this phase delay into its calculations.

Two sets of registers allow for two distinct filter responses. The main filter, called the normal mode filter, is controlled by programming Register 0x60 to Register 0x63. The other filter, called the light load mode filter, is controlled by programming Register 0x64 to Register 0x67. The ADP1043A uses the light load mode filter only when the modulation is below the load current threshold (programmed through Register 0x3B).

The Analog Devices software GUI allows the user to program the light load mode filter in the same manner as the normal mode filter. It is recommended that the GUI be used for this purpose.

In addition, during the soft start process, a different set of digital filters is used. The soft start filter value for a, b, and c in Equation 1 is 0, and the d value is programmed through the soft start filter gain setting (Register 0x5F[1:0]).

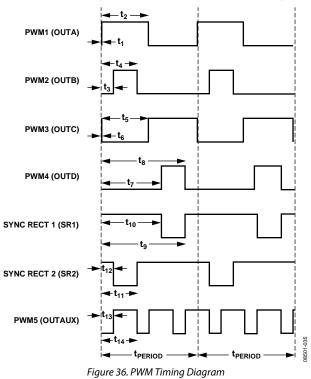

# PWM AND SYNC RECT OUTPUTS (OUTA, OUTB, OUTC, OUTD, OUTAUX, SR1, SR2)

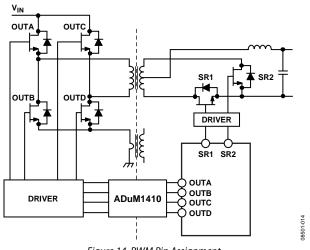

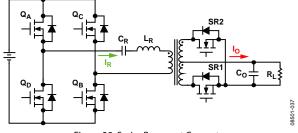

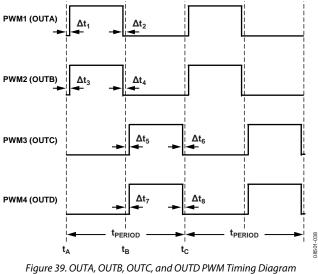

The PWM and SR outputs are used for control of the primary side drivers and the synchronous rectifier drivers. These outputs can be used for several control topologies, including full-bridge, phase-shifted ZVS, and interleaved two switch forward converter configurations. Delays between rising and falling edges can be individually programmed. Special care must be taken to avoid shoot-through and cross-conduction. It is recommended that the Analog Devices software GUI be used to program these outputs. Figure 14 shows an example configuration to drive a full-bridge, phase shift topology with synchronous rectification.

Figure 14. PWM Pin Assignment

The PWM and SR outputs all work together. Therefore, when reprogramming more than one of these outputs, it is important to first update all the registers, and then latch the information into the ADP1043A at one time. During reprogramming, the outputs are temporarily disabled. A special instruction is sent to the ADP1043A to ensure that new timing information is programmed simultaneously. This is done by setting Register 0x5D[0] to 1. It is recommended that PWM outputs be disabled when not in use.

OUTAUX is an additional PWM output pin; OUTAUX allows an extra PWM signal to be generated at a different frequency from the other six PWM outputs. This signal can be used to drive an extra power converter stage, such as a buck controller located in front of a full-bridge converter. OUTAUX can also be used as a clock reference signal.

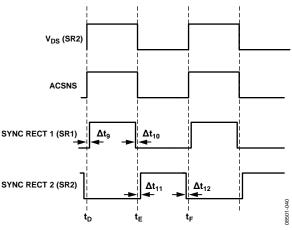

### SYNCHRONOUS RECTIFICATION

SR1 and SR2 are recommended for use as the PWM control signals when using synchronous rectification. These PWM signals can be set up similarly to the other PWM outputs. The turn-on of these signals can be programmed in two ways. They can either be turned on to their full PWM value immediately, or they can be turned on in a soft start fashion. When turned on in a soft start, the signals ramp up from zero duty cycle to the desired duty cycle. The advantage of ramping the SR signals is to minimize a voltage step that would occur by turning the SR FETs on completely. The advantage of turning the SR signals completely on immediately is that they can help to minimize the voltage transient caused by a load step.

Using Register 0x54[1], the SR soft start can be programmed to occur just once, the first time that the SR signals are enabled, or every time that the SR signals are enabled.

When programming the ADP1043A to use SR soft start, ensure correct operation of this function by setting the falling edge of SR1 ( $t_{10}$ ) to a lower value than the rising edge of SR1 ( $t_9$ ) and by setting the falling edge of SR2 ( $t_{12}$ ) to a lower value than the rising edge of SR2 ( $t_{11}$ ).

The speed of the SR enable is approximately 200 µs. This ensures that in case of a load step, the SR signals (and any other PWM outputs that are temporarily disabled) can be turned on quickly enough to prevent damage to the FETs that they are controlling.

#### ADAPTIVE DEAD TIME CONTROL

A set of registers called the adaptive dead time (ADT) registers (Register 0x68 to Register 0x6F) allows the dead time between PWM edges to be adapted on-the-fly. The ADP1043A uses the ADT only when the modulation is below the dead time (load current) threshold (programmed in Register 0x68). The Analog Devices software GUI allows the user to easily program the dead time values, and it is recommended that the software be used for that purpose.

Each individual PWM rising and falling edge ( $t_1$  to  $t_{14}$ ) can then be programmed to have a specific dead time offset. This offset can be positive or negative. The offset is relative to the nominal edge position. For example, if  $t_1$  has a nominal rising edge of 100 ns and the ADT setting for  $t_1$  is -15 ns,  $t_1$  moves to 85 ns when it falls below the adaptive dead time threshold. The dead times are programmed using Register 0x69 to Register 0x6F.

# LIGHT LOAD MODE

Register 0x3B allows the ADP1043A to shut down PWM outputs under light load conditions. The light load current threshold can be programmed. Below this current threshold, the SR outputs are disabled. The user can also program any of the other PWM outputs to shut down below this current threshold. This allows the ADP1043A to be used with an interleaved two transistor forward topology, incorporating phase shedding at light load. The light load mode digital filter is also used during light load mode.

#### **MODULATION LIMIT**

Using the modulation limit register (Register 0x2E), it is possible to apply a maximum modulation limit and a minimum modulation limit to any PWM signal, thus limiting the modulation range of any PWM. These limits are a percentage of the switching period. If the modulation required is lower than the minimum setting, pulse skipping can be enabled.

Following is an example of how to use the modulation limit settings. In this example, the switching cycle period is 4  $\mu$ s and modulation on the t<sub>2</sub> edge (falling edge) is enabled. The nominal position of t<sub>2</sub> is set to 1.6  $\mu$ s, which is 40% of the 4  $\mu$ s period. The modulation high limit is set to (nominal + 50%). Therefore, the modulation high limit is (40% + 50%) = 90% of the switching cycle period; 90% of 4  $\mu$ s = 3.6  $\mu$ s. The modulation low limit is set to (nominal – 35%). Therefore, the modulation low limit is (40% – 35%) = 5% of the switching cycle period; 5% of 4  $\mu$ s = 0.2  $\mu$ s.

The GUI provided with the ADP1043A is recommended for evaluating this feature of the ADP1043A (see Figure 15).

Figure 15. Setting Modulation Limits (Modulation Range Shown by Arrows)

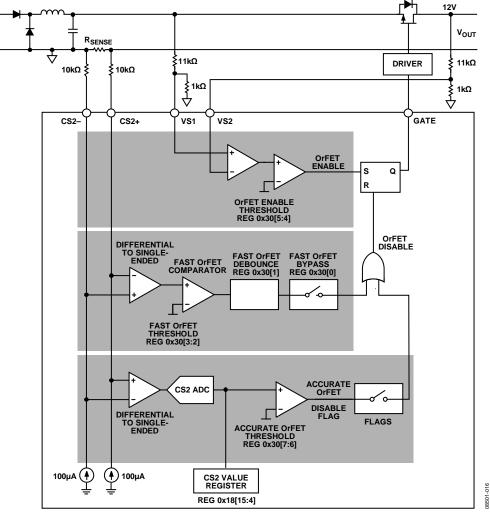

# **OrFET CONTROL (GATE)**

The GATE control signal drives an external OrFET. The OrFET gate control is used to protect against power flow into the power supply from another supply. This ensures that power flows only out of the power supply and that the unit can be hot-swapped. The OrFET circuit can be used only when the ADP1043A is connected to a sense resistor on the low side. The OrFET circuit is not guaranteed for operation with high-side current sensing.

The GATE pin is an open-drain, N-channel MOSFET. An external 2.2 k $\Omega$  pull-up resistor is recommended. Its output is normally high to keep the OrFET turned off. When the start-up criteria have been achieved, the GATE output is pulled low, allowing the OrFET to turn on. The OrFET turn-on and turn-off thresholds can be individually programmed. The GATE outputs are CMOS levels (0 V to 3.3 V). An external driver is required to turn the OrFET on or off.

The OrFET can be turned off by three methods:

- Fault flag (any fault flag can be programmed to turn off the OrFET)

- Fast OrFET control circuit

- Accurate OrFET control circuit

Fast OrFET control looks at the reverse voltage across CS2+ and CS2– and is implemented using an analog comparator (see Figure 16). If the voltage difference between CS2+ and CS2– is greater than the fast OrFET threshold programmed in Register 0x30, the OrFET is turned off.

Accurate OrFET control also uses the reverse voltage across the CS2+ and CS2– pins to disable the OrFET (see Figure 16). If the voltage difference between CS2+ and CS2– is greater than 0 mV, the OrFET is disabled. The accurate OrFET circuit is more accurate, but it is slower than the fast OrFET circuit.

The OrFET turn-on circuit looks at the voltage difference between VS1 and VS2 (see Figure 16). When the forward voltage drop from VS1 to VS2 is greater than the programmable OrFET enable threshold (Register 0x30[5:4]), the OrFET is enabled. The OrFET enable threshold can be set to -0.5%, 0%, 1%, or 2% of the nominal output voltage (12 V).

#### **Recommended Setup**

In a 12 V application, while in normal operating mode

- When 12 V < V<sub>OUT</sub> < OVP, use the accurate OrFET control circuit to turn off the OrFET.

- When V<sub>OUT</sub> > OVP, use load OVP to turn off the OrFET.

In a 12 V application, while in light load mode

- When 12 V < V<sub>OUT</sub> < OVP, use ACSNS to turn off the OrFET.

- When V<sub>OUT</sub> > OVP, use load OVP to turn off the OrFET.

In a 12 V application, when an internal short circuit occurs, follow this procedure:

- 1. Use fast OrFET to turn off the OrFET.

- 2. Use CS1 OCP or VS1 UVP to shut down the unit and restart it.

Figure 16. OrFET Control Circuit Internal Detailed Diagram

#### **OrFET Operation Examples**

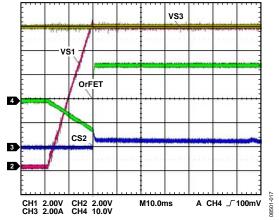

#### Hot Plug into a Live Bus

A new PSU is plugged into a live 12 V bus (yellow). The internal voltage VS1 (red) is ramped up before the OrFET is turned on. After the OrFET is turned on (green), current in the new PSU begins to flow to the load (blue). The turn-on voltage threshold between the new PSU and the bus is programmable.

Figure 17. Hot Plug into a Live Bus (Yellow Is Bus Voltage; Red Is VS1 Voltage; Green Is OrFET Control Signal; Blue Is Load Current)

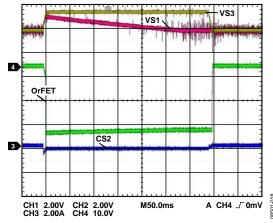

#### **Runaway Master**

A rogue PSU on the bus (yellow) has a fault condition, and the result is that the bus voltage increases above the OVP threshold. The good PSU turns off the OrFET (green) and regulates its internal voltage VS1 (red). When the rogue power supply fault condition is removed, the bus voltage decreases. The OrFET of the good PSU is immediately turned on and the good PSU resumes regulating from VS3.

Figure 18. Runaway Master (Yellow Is Bus Voltage; Red Is VS1 Voltage; Green Is OrFET Control Signal; Blue Is Load Current)

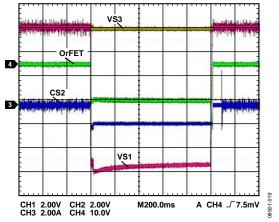

#### Short Circuit

When one of the output rectifiers fails, the bus voltage can collapse if the OrFET is not promptly turned off. The fast OrFET comparator is used to protect the system from this fault event. Figure 19 shows a short circuit applied to the output capacitors, before the OrFET. After the fast OrFET threshold for CS2 (blue) is triggered, the OrFET (green) is turned off. In this case, the gate driver is not very fast and takes about 500 ns. (A larger buffer to drive the OrFET would turn it off quicker.) Figure 19 also shows the operation when the short circuit is removed. The internal regulation point, VS1 (red), returns to 12 V, and the OrFET (green) is reenabled. The PSU again begins to contribute current to the load (blue).

Figure 19. Internal Short Circuit (Yellow Is Bus Voltage; Red Is VS1 Voltage; Green Is OrFET Control Signal; Blue Is Load Current)

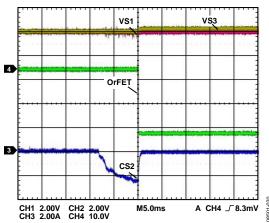

#### Light Load Mode Operation

PSU 1 increases its voltage at light load from 12 V to 12.1 V (yellow). Both PSU 1 and PSU 2 are CCM, so PSU 1 sources current and PSU 2 sinks current (blue). In PSU 2, after 10 ms the accurate OrFET control turns off the OrFET to prevent reverse current from flowing. Note that the OrFET voltage (green) is solid during this transition because PSU 1 and PSU 2 are in CCM mode.

Figure 20. Light Load Mode (Yellow Is Bus Voltage; Red Is VS1 Voltage; Green Is OrFET Control Signal; Blue Is Load Current)

# VDD

When VDD is applied, a certain time elapses before the part is capable of regulating the power supply. When the VDD rises above the power-on reset and UVLO levels, it takes approximately 20  $\mu$ s for VCORE to reach its operational point of 2.5 V. The EEPROM contents are then downloaded to the registers. The download takes an additional 25  $\mu$ s (approximately). After the EEPROM download, the ADP1043A is ready for operation. If the ADP1043A is programmed to power up at this time, the soft start ramp begins.

# **VDD/VCORE OVLO**

The ADP1043A has built-in overvoltage protection (OVP) on its supply rails. When the VDD or VCORE voltage rises above the OVLO threshold, the response can be programmed. This circuit can be set to be ignored, but it is recommended that the user not program the OVP circuit to be ignored.

# **POWER GOOD**

The ADP1043A has two power-good pins. The PGOOD1 pin and fault flag are set when any of the following conditions are out of range: power supply, CS1 fast OCP, CS1 accurate OCP, CS2 accurate OCP, UVP, local OVP, or load OVP.

The PGOOD2 pin and fault flag are set when any flag is set: power supply, OrFET, CS1 fast OCP, CS1 accurate OCP, CS2 accurate OCP, voltage continuity, UVP, accurate OrFET disable, ACSNS, external flag (FLAGIN), VCORE OV, VDD OV, local OVP, load OVP, OTP, CRC fault, and EEPROM unlocked.

If Register 0x2D[3] is set, PGOOD2 looks only at the flags that are not programmed to be ignored.

The PGOOD2 pin can also be used as an interrupt pin to notify a host controller that a flag has been set. The polarity of the PGOOD1 and PGOOD2 pins is configured as active low.

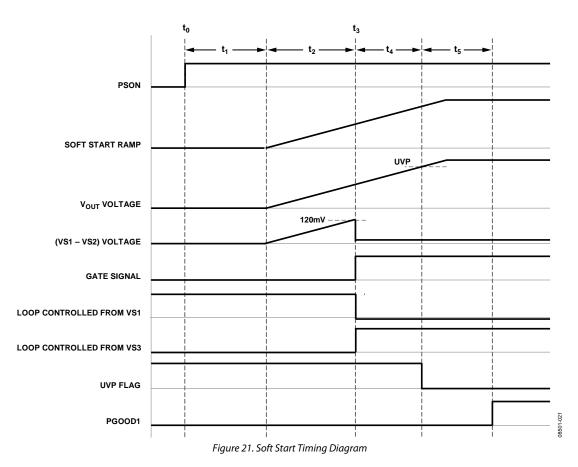

### SOFT START

A dedicated filter is used during soft start. The filter is disabled at the end of the soft start routine, and the voltage loop digital filter is used.

#### Fault Condition During Soft Start

If a CS1 fast OCP fault condition occurs during soft start, the entire soft start routine is reset, and the ADP1043A begins another soft start routine. All other fault flags are ignored during soft start.

#### Soft Start Routine

When the user turns on the power supply (enables PSON), the following soft start procedure occurs:

- The PSON signal is enabled at Time t<sub>0</sub>. The ADP1043A checks that initial flags are OK. These flags include VDD OK and GND OK.

- 2. The ADP1043A waits for Time  $t_1$  before it begins soft start. The length of  $t_1$  is set in Register 0x2C, Bits[4:3].

- 3. The soft start begins to ramp up the power supply voltage at the start of Time  $t_2$ .

- 4. The ADP1043A keeps the OrFET gate signal turned off. The voltage differential across the OrFET increases (VS1 – VS2) due to the diode conduction of the OrFET. When the voltage differential reaches the OrFET enable threshold (Register 0x30, Bits[5:4]), the OrFET gate signal is enabled at Time t<sub>3</sub>. The ADP1043A begins to regulate voltage from VS3 instead of VS1.

- 5. After the power supply voltage increases above the VS1 UVP undervoltage limit (Register 0x34, Bits[6:0]), at the end of Time t<sub>4</sub>, the UVP flag is reset.

- 6. After the UVP flag is reset and if all other PGOOD1 fault conditions are OK, the PGOOD1 signal waits for Time  $t_5$  before it is enabled. The length of  $t_5$  is programmable in Register 0x2D, Bits[7:4].

### **CURRENT SHARING (SHARE)**

The ADP1043A supports both analog current sharing and digital current sharing. It is recommended that analog current sharing be used because it offers improved performance over digital current sharing. Digital current sharing requires a load line of >15 m $\Omega$  to prevent oscillation between units. The analog current sharing scheme has no such issues.

Using Register 0x29, Bit 3, it is possible to program the ADP1043A to use the CS1 current information or the CS2 current information for current sharing.

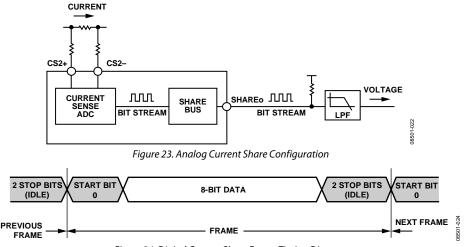

#### **Analog Current Sharing**

The ADP1043A supports analog current sharing. The current reading from CS1 or CS2 can be output to the SHAREo pin in the form of a digital bit stream, which is the output of the current sense ADC (see Figure 23). The bit stream is proportional to the current being delivered by this unit to the load. By filtering this digital bit stream using an external RC filter, the current information is turned into an analog voltage. This means that there is now an analog voltage that is proportional to the current being delivered by this unit to the load. This voltage can be compared to the share bus. If the unit is not supplying enough current, an error signal can be applied to the VS3 feedback point. This signal causes the unit to increase its output voltage and, therefore, its current contribution to the load.

For more information about the analog current share functionality, including schematics and measurements in different fault and setup conditions, see the product page for the ADP1043A.

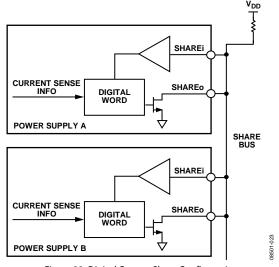

#### **Digital Share Bus**

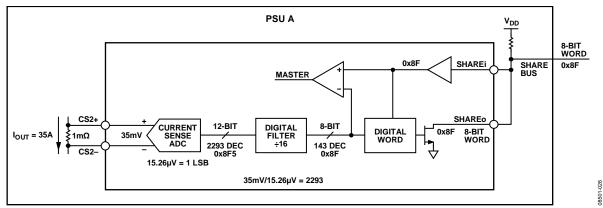

The digital share bus scheme is similar in principle to the traditional analog share bus scheme. The difference is that instead of using a voltage on the share bus to represent current, a digital word is used.

The ADP1043A outputs a digital word onto the share bus. The digital word is a function of the current that the power supply is providing (the higher the current, the larger the digital word).

The power supply with the highest current controls the bus (master). A power supply that is putting out less current (slave) sees that another supply is providing more power to the load than it is. During the next cycle, the slave increases its current output contribution by increasing its output voltage. This cycle continues until the slave outputs the same current as the master, within a programmable tolerance range. Figure 22 shows the configuration of the digital share bus.

Figure 22. Digital Current Share Configuration

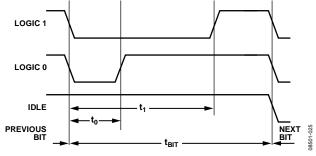

The digital share bus is based on a single-wire communication bus principle; that is, the clock and data signals are contained together.