**LMV641**

SNOSAW3D - SEPTEMBER 2007 - REVISED AUGUST 2016

# LMV641 10-MHz, 12-V, Low-Power Amplifier

#### **Features**

Specified for 2.7-V, and ±5-V Performance

Low Power Supply Current: 138 µA High Unity Gain Bandwidth: 10 MHz Max Input Offset Voltage: 500 μV

CMRR: 120 dB PSRR: 105 dB

Input Referred Voltage Noise: 14 nV/√Hz

1/f Corner Frequency: 4 Hz

Output Swing With 2-kΩ Load 40 mV from Rail

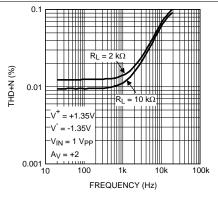

Total Harmonic Distortion: 0.002% at 1 kHz, 2 k $\Omega$

Temperature Range -40°C to 125°C

## **Applications**

- Portable Equipment

- **Battery-Powered Systems**

- Sensors and Instrumentation

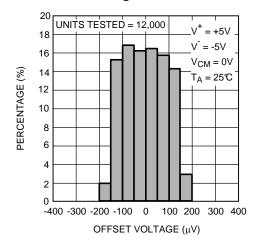

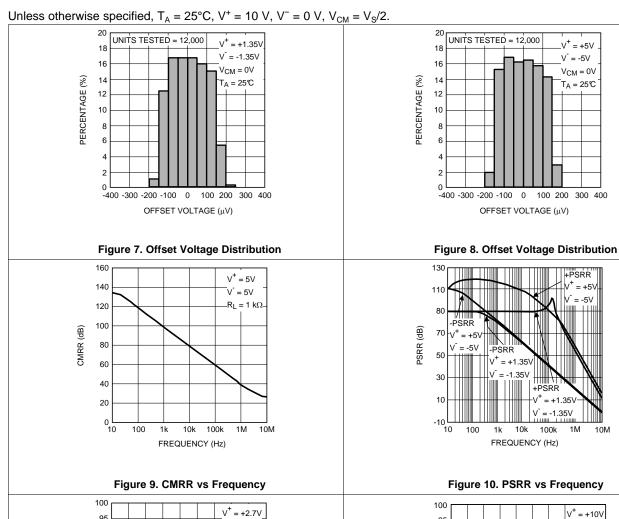

## Offset Voltage Distribution

## 3 Description

The LMV641 is a low-power, wide-bandwidth operational amplifier with an extended power supply voltage range of 2.7 V to 12 V.

The device features 10 MHz of gain bandwidth product with unity gain stability on a typical supply current of 138 µA. Other key specifications are a PSRR of 105 dB, CMRR of 120 dB,  $V_{OS}$  of 500  $\mu V$ , input referred voltage noise of 14 nV/ $\sqrt{\text{Hz}}$ , and a THD of 0.002%. This amplifier has a rail-to-rail output stage and a common mode input voltage, which includes the negative supply.

The LMV641 device operates over a temperature range of -40°C to +125°C and is offered in the boardspace-saving 5-Pin SC70, SOT-23, and 8-Pin SOIC packages.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

|             | SOIC (8)   | 4.90 mm × 3.91 mm |

| LMV641      | SOT-23 (5) | 2.90 mm × 1.60 mm |

|             | SC70 (5)   | 2.00 mm × 1.25 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

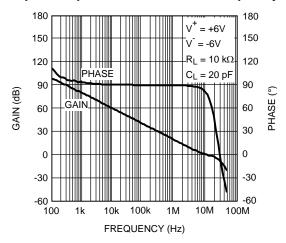

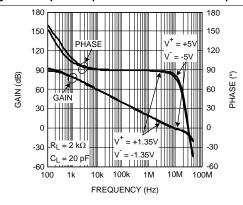

#### Open Loop Gain and Phase vs Frequency

#### **Table of Contents**

| 1 | Features 1                               |    | 7.4 Device Functional Modes                         | 15    |

|---|------------------------------------------|----|-----------------------------------------------------|-------|

| 2 | Applications 1                           | 8  | Application and Implementation                      | 17    |

| 3 | Description 1                            |    | 8.1 Application Information                         | 17    |

| 4 | Revision History2                        |    | 8.2 Typical Applications                            | 17    |

| 5 | Pin Configuration and Functions          | 9  | Power Supply Recommendations                        |       |

| 6 | Specifications4                          | 10 | Layout                                              | 23    |

| • | 6.1 Absolute Maximum Ratings             |    | 10.1 Layout Guidelines                              | 23    |

|   | 6.2 ESD Ratings                          |    | 10.2 Layout Example                                 | 23    |

|   | 6.3 Recommended Operating Conditions     | 11 | Device and Documentation Support                    | 24    |

|   | 6.4 Thermal Information                  |    | 11.1 Device Support                                 | 24    |

|   | 6.5 DC Electrical Characteristics: 2.7 V |    | 11.2 Documentation Support                          | 24    |

|   | 6.6 DC Electrical Characteristics: 10 V  |    | 11.3 Receiving Notification of Documentation Update | es 24 |

|   | 6.7 Typical Characteristics 8            |    | 11.4 Community Resource                             | 24    |

| 7 | Detailed Description 14                  |    | 11.5 Trademarks                                     | 24    |

| - | 7.1 Overview                             |    | 11.6 Electrostatic Discharge Caution                | 24    |

|   | 7.2 Functional Block Diagram             |    | 11.7 Glossary                                       | 24    |

|   | 7.3 Feature Description                  | 12 | Mechanical, Packaging, and Orderable Information    | 25    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

##

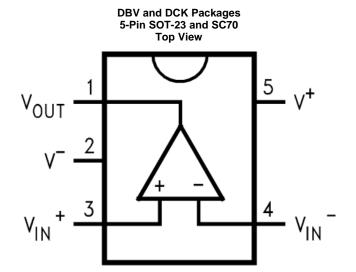

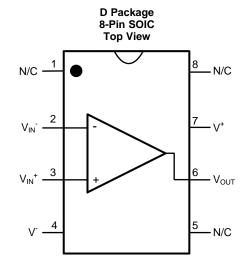

# 5 Pin Configuration and Functions

#### **Pin Functions**

|                   |        | PIN  |      | TYPE <sup>(1)</sup> | DESCRIPTION           |  |  |  |  |  |  |  |  |

|-------------------|--------|------|------|---------------------|-----------------------|--|--|--|--|--|--|--|--|

| NAME              | SOT-23 | SC70 | SOIC | I TPE'              | DESCRIPTION           |  |  |  |  |  |  |  |  |

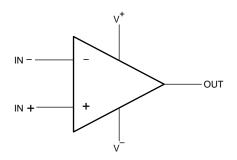

| V <sub>IN</sub> + | 3      | 3    | 3    | I                   | Noninverting Input    |  |  |  |  |  |  |  |  |

| V <sub>IN</sub> - | 4      | 4    | 2    | I                   | Inverting Input       |  |  |  |  |  |  |  |  |

| V <sub>OUT</sub>  | 1      | 1    | 6    | 0                   | Output                |  |  |  |  |  |  |  |  |

| V*                | 5      | 5    | 7    | Р                   | Positive supply input |  |  |  |  |  |  |  |  |

| V <sup>-</sup>    | 2      | 2    | 4    | Р                   | Supply negative input |  |  |  |  |  |  |  |  |

(1) I = input; O = output; P = power

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                       | MIN                   | MAX                 | UNIT |

|---------------------------------------|-----------------------|---------------------|------|

| Differential input V <sub>ID</sub>    | ±0.3                  | ±0.3                | V    |

| Supply voltage $(V_S = V^+ - V^-)$    |                       | 13.2                | V    |

| Input and output pin voltage          | (V <sup>-</sup> -0.3) | V <sup>+</sup> +0.3 | V    |

| Junction temperature (3)              |                       | 150                 | °C   |

| Storage temperature, T <sub>stg</sub> | -65                   | 150                 | °C   |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For ensured specifications and the test conditions, see the *Electrical Characteristics* Tables.

- (2) If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office / Distributors for availability and specifications.

- (3) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PC board.

## 6.2 ESD Ratings

|                    |                         |                             | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------|-------|------|

| .,                 | Floatroatatia diasharas | Human-body model (HBM), (1) | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Machine model (MM)          | ±200  | V    |

<sup>(1)</sup> Human Body Model, applicable std. MIL-STD-883, Method 3015.7.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                    | MIN | NOM MAX | UNIT |

|------------------------------------|-----|---------|------|

| Temperature <sup>(1)</sup>         | -40 | 125     | °C   |

| Supply voltage $(V_S = V^+ - V^-)$ | 2.7 | 12      | V    |

<sup>(1)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta,JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta,JA}$ . All numbers apply for packages soldered directly onto a PC board.

#### 6.4 Thermal Information

|                                 |                                              | LMV641       |            |          |      |  |

|---------------------------------|----------------------------------------------|--------------|------------|----------|------|--|

|                                 | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT-23) | DCK (SC70) | D (SOIC) | UNIT |  |

|                                 |                                              | 5 PINS       | 5 PINS     | 8 PINS   |      |  |

| R <sub>0JA</sub> <sup>(2)</sup> | Junction-to-ambient thermal resistance       | 325          | 456        | 166      | °C/W |  |

| $R_{\theta JC(top)}$            | Junction-to-case (top) thermal resistance    | 178.1        | 121.8      | 93.6     | °C/W |  |

| $R_{\theta JB}$                 | Junction-to-board thermal resistance         | 60.8         | 68.9       | 90.9     | °C/W |  |

| ΨЈТ                             | Junction-to-top characterization parameter   | 57.7         | 5.3        | 38.4     | °C/W |  |

| ΨЈВ                             | Junction-to-board characterization parameter | 60.2         | 68.1       | 90.4     | °C/W |  |

| $R_{\theta JC(bot)}$            | Junction-to-case (bottom) thermal resistance | n/a          | n/a        | n/a      | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: LMV641

<sup>(2)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta,JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta,JA}$ . All numbers apply for packages soldered directly onto a PC board.

## 6.5 DC Electrical Characteristics: 2.7 V

Unless otherwise specified, all limits are specified for  $T_A$  = 25°C,  $V^+$  = 2.7 V,  $V^-$  = 0 V,  $V_O$  =  $V_{CM}$  =  $V^+/2$ , and  $R_L$  > 1 M $\Omega$ .

|                    | PARAMETER                    | TEST CO                                                                                                                 | NDITIONS                             | MIN<br>(1) | TYP    | MAX<br>(1) | UNIT               |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------|--------|------------|--------------------|

| V                  | Input offset voltage         | T <sub>A</sub> = 25°C                                                                                                   |                                      |            | 30     | 500        | μV                 |

| V <sub>OS</sub>    | Input offset voltage         | Temperature extremes                                                                                                    |                                      |            |        | 750        | μν                 |

| TC V <sub>OS</sub> | Input offset average drift   |                                                                                                                         |                                      | 0.1        |        | μV/°C      |                    |

|                    | lanut bina aumant            | $T_A = 25^{\circ}C^{(3)}$                                                                                               |                                      | 75         | 95     | ^          |                    |

| I <sub>B</sub>     | Input bias current           | Temperature extremes                                                                                                    |                                      |            |        | 110        | nA                 |

| Ios                | Input offset current         |                                                                                                                         |                                      |            | 0.9    | 5          | nA                 |

| CMRR               | Common-mode rejection        | 0 V ≤ V <sub>CM</sub> ≤ 1.7 V                                                                                           | $T_A = 25^{\circ}C^{(3)}$            | 89         | 114    |            | dB                 |

| CIVIKK             | ratio                        | 0 V = V <sub>CM</sub> = 1.7 V                                                                                           | Temperature extremes                 | 84         |        |            | uБ                 |

|                    |                              | $2.7 \text{ V} \le \text{V}^+ \le 10 \text{ V}, \text{V}_{CM} =$                                                        | $T_A = 25^{\circ}C^{(3)}$            | 94.5       | 105    |            |                    |

| DCDD               | Dower cumply rejection retio | 0.5                                                                                                                     | Temperature extremes                 | 92.5       |        |            | dB                 |

| PSRR               | Power supply rejection ratio | $2.7 \text{ V} \le \text{V}^+ \le 12 \text{ V}, \text{ V}_{\text{CM}} =$                                                | $T_A = 25^{\circ}C^{(3)}$            | 94         | 100    |            | иь                 |

|                    |                              | 0.5                                                                                                                     | Temperature extremes                 | 92         |        |            |                    |

| CMVR               | Input common-mode            | CMRR ≥ 80 dB                                                                                                            | $T_A = 25^{\circ}C^{(3)}$            | 0          |        | 1.8        | M                  |

| CMVR               | voltage range                |                                                                                                                         |                                      |            |        |            | V                  |

|                    |                              | $0.3 \text{ V} \le \text{V}_{\text{O}} \le 2.4 \text{ V}, \text{R}_{\text{L}} = 2 \text{ k}\Omega \text{ to V}^{+}/2$   |                                      | 82         | 88     |            |                    |

|                    |                              | $0.4 \text{ V} \le \text{V}_{\text{O}} \le 2.3 \text{ V}, \text{R}_{\text{L}} = 2.3 \text{ V}$                          | 2 kΩ to V <sup>+</sup> /2            | 78         |        |            |                    |

| A <sub>VOL</sub>   | Large signal voltage gain    | $0.3 \text{ V} \le \text{V}_{\text{O}} \le 2.4 \text{ V}, \text{ R}_{\text{L}} = 10 \text{ k}\Omega \text{ to V}^{+}/2$ | T <sub>A</sub> = 25°C <sup>(3)</sup> | 86         | 98     |            | dB                 |

|                    |                              | $0.4 \text{ V} \le \text{V}_{\text{O}} \le 2.3 \text{ V}, \text{ R}_{\text{L}} = 10 \text{ k}\Omega \text{ to V}^{+/2}$ | Temperature extremes                 | 82         |        |            |                    |

|                    |                              | $R_L = 2 k\Omega$ to $V^+/2$ , $V_{IN} =$                                                                               | $T_A = 25^{\circ}C^{(3)}$            |            | 42     | 58         |                    |

|                    |                              | 100 mV                                                                                                                  | Temperature extremes                 |            |        | 68         |                    |

|                    | Output swing high            | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2, V_{IN} =$                                                                   | $T_A = 25^{\circ}C^{(3)}$            |            | 22     | 35         |                    |

|                    |                              | 100 mV                                                                                                                  | Temperature extremes                 |            |        | 40         | mV from            |

| V <sub>O</sub>     |                              | $R_L = 2 k\Omega$ to $V^+/2$ , $V_{IN} =$                                                                               | $T_A = 25^{\circ}C^{(3)}$            |            | 38     | 48         | rail               |

|                    | Outside soles law            | 100 mV                                                                                                                  | Temperature extremes                 |            |        | 58         |                    |

|                    | Output swing low             | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2, V_{IN} =$                                                                   |                                      |            | 18     | 30         |                    |

|                    |                              | 100 mV                                                                                                                  |                                      |            |        | 35         |                    |

|                    | Sourcing and sinking output  | $V_{IN}$ DIEE = 100 mV to $V_{O}$                                                                                       | Sourcing                             |            | 22     |            |                    |

| I <sub>OUT</sub>   | current                      | $V_{IN\_DIFF} = 100 \text{ mV to } V_O$<br>= $V^+/2^{(4)}$                                                              | Sinking                              |            | 25     |            | mA                 |

|                    |                              | T <sub>A</sub> = 25°C <sup>(3)</sup>                                                                                    |                                      |            | 138    | 170        |                    |

| I <sub>S</sub>     | Supply current               | Temperature extremes                                                                                                    |                                      |            | 220    | μΑ         |                    |

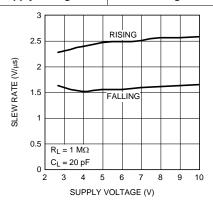

| 0.0                | 01 .                         | A 4 1/4 / 1/4                                                                                                           | Rising (10% to 90%)                  |            | 2.3    |            |                    |

| SR                 | Slew rate                    | $A_V = 1$ , $V_O = 1$ $V_{PP}$                                                                                          | Falling (90% to 10%)                 |            | 1.6    |            | V/µs               |

| GBW                | Gain bandwidth product       |                                                                                                                         |                                      |            | 10     |            | MHz                |

| e <sub>n</sub>     | Input-referred voltage noise | f = 1 kHz                                                                                                               |                                      |            | 14     |            | nV/√ <del>Hz</del> |

| i <sub>n</sub>     | Input-referred current noise | f = 1 kHz                                                                                                               |                                      |            | 0.15   |            | pA/√ <del>Hz</del> |

| THD                | Total harmonic distortion    | $f = 1 \text{ kHz}, A_V = 2, R_L = 2 \text{ kHz}$                                                                       | (Ω                                   |            | 0.014% |            |                    |

Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlations using Statistical Quality Control (SQC) method.

Product Folder Links: LMV641

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

<sup>(3)</sup> Positive current corresponds to current flowing into the device.

<sup>(4)</sup> The part is not short-circuit protected and is not recommended for operation with low resistive loads. Typical sourcing and sinking output current curves are provided in *Typical Characteristics* and should be consulted before designing for heavy loads.

#### 6.6 DC Electrical Characteristics: 10 V

Unless otherwise specified, all limits are specified for  $T_A = 25$ °C,  $V^+ = 10$  V,  $V^- = 0$  V,  $V_O = V_{CM} = V^+/2$ , and  $R_L > 1$  M $\Omega$ .

|                                      | PARAMETER                       | TEST COND                                                                                                               | ITIONS                               | MIN<br>(1) | TYP    | MAX<br>(1) | UNIT    |  |

|--------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------|--------|------------|---------|--|

| V <sub>OS</sub> Input offset voltage |                                 | T <sub>A</sub> = 25°C <sup>(3)</sup>                                                                                    |                                      |            | 5      | 500        | /       |  |

| V <sub>OS</sub>                      | Input offset voltage            | Temperature extremes                                                                                                    |                                      |            |        | 750        | μV      |  |

| TC V <sub>OS</sub>                   | Input offset average drift      |                                                                                                                         |                                      |            | 0.1    |            | μV/°C   |  |

|                                      |                                 |                                                                                                                         | $T_A = 25^{\circ}C^{(3)}$            |            | 70     | 90         |         |  |

| l <sub>B</sub>                       | Input bias current              | (3)                                                                                                                     | Temperature extremes                 |            |        | 105        | nA      |  |

| los                                  | Input offset current            |                                                                                                                         |                                      |            | 0.7    | 5          | nA      |  |

|                                      | Common-mode rejection           |                                                                                                                         | $T_A = 25^{\circ}C^{(3)}$            | 94         | 120    |            |         |  |

| CMRR                                 | ratio                           | 0 V ≤ V <sub>CM</sub> ≤ 9 V                                                                                             | Temperature extremes                 | 90         |        |            | dB      |  |

|                                      |                                 | 271/21/12/101/11/05                                                                                                     | $T_A = 25^{\circ}C^{(3)}$            | 94.5       | 105    |            |         |  |

| DODD                                 | Power supply rejection          | $2.7 \text{ V} \le \text{V}^+ \le 10 \text{ V}, \text{ V}_{\text{CM}} = 0.5 \text{ V}$                                  | Temperature extremes                 | 92.5       |        |            | .ID     |  |

| PSRR                                 | ratio                           | 271/21/42/12/1                                                                                                          | T <sub>A</sub> = 25°C <sup>(3)</sup> | 94         | 100    |            | dB      |  |

|                                      |                                 | $2.7 \text{ V} \le \text{V}^+ \le 12 \text{ V}, \text{ V}_{\text{CM}} = 0.5 \text{ V}$                                  | Temperature extremes                 | 92         |        |            |         |  |

| lanut and                            | Innut common mode               | CMRR ≥ 80 dB                                                                                                            | $T_A = 25^{\circ}C^{(3)}$            | 0          |        | 9.1        |         |  |

| CMVR                                 | Input common-mode voltage range | CMRR ≥ 76 dB                                                                                                            | Temperature extremes                 | 0          |        | 9.1        | V       |  |

|                                      |                                 | $0.3 \text{ V} \le \text{V}_{\text{O}} \le 9.7 \text{ V}, \text{R}_{\text{L}} = 2$                                      | $T_A = 25^{\circ}C^{(3)}$            | 90         | 99     |            |         |  |

|                                      | Large signal voltage gain       | $k\Omega$ to V <sup>+</sup> /2<br>0.4 V ≤ V <sub>O</sub> ≤ 9.6 V, R <sub>L</sub> = 2<br>$k\Omega$ to V <sup>+</sup> /2  | Temperature extremes                 | 85         |        |            |         |  |

| A <sub>VOL</sub>                     |                                 | $0.3 \text{ V} \le \text{V}_{\text{O}} \le 9.7 \text{ V}, \text{R}_{\text{L}} = 10$                                     | T <sub>A</sub> = 25°C <sup>(3)</sup> | 97         | 97 104 |            | dB      |  |

|                                      |                                 | $k\Omega$ to V <sup>+</sup> /2<br>0.4 V ≤ V <sub>O</sub> ≤ 9.6 V, R <sub>L</sub> = 10<br>$k\Omega$ to V <sup>+</sup> /2 | Temperature extremes                 | 92         |        |            |         |  |

|                                      |                                 |                                                                                                                         | T <sub>A</sub> = 25°C <sup>(3)</sup> |            | 68     | 95         |         |  |

|                                      |                                 | $R_L = 2 \text{ k}\Omega \text{ to V}^+/2, V_{IN} = 100$ mV                                                             | Temperature extremes                 |            |        | 125        |         |  |

|                                      | Output Swing High               | D 401015 V/t/0 V/ 400                                                                                                   | $T_A = 25^{\circ}C^{(3)}$            |            | 37     | 55         |         |  |

| .,                                   |                                 | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2, V_{IN} = 100 \text{ mV}$                                                    | Temperature extremes                 |            |        | 65         | mV fror |  |

| Vo                                   |                                 | D 01:0 to 1/1/0 1/ 400                                                                                                  | $T_A = 25^{\circ}C^{(3)}$            |            | 65     | 90         | rail    |  |

|                                      | Outrot Code a Lavo              | $R_L = 2 \text{ k}\Omega \text{ to V}^+/2, V_{IN} = 100$ mV                                                             | Temperature extremes                 |            |        | 110        |         |  |

|                                      | Output Swing Low                | P = 10 kO to \/ <sup>+</sup> /2 \/ = 100                                                                                | $T_A = 25^{\circ}C^{(3)}$            |            | 32     | 42         |         |  |

|                                      |                                 | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2, V_{IN} = 100 \text{ mV}$                                                    | Temperature extremes                 |            |        | 52         |         |  |

| lou-                                 | Sourcing and sinking            | V <sub>IN_DIFF</sub> = 100 mV                                                                                           | Sourcing                             |            | 26     |            | mA      |  |

| l <sub>OUT</sub>                     | output current                  | to $V_0 = V^+/2^{-(4)}$                                                                                                 | Sinking                              |            | 112    |            | 1117    |  |

| I <sub>S</sub>                       | Supply current                  | $T_A = 25^{\circ}C^{(3)}$                                                                                               |                                      |            | 158    | 190        | μA      |  |

| .9                                   | Cappi, canoni                   | Temperature extremes                                                                                                    |                                      |            | 240    | μ, ,       |         |  |

| SR                                   | Slew rate                       | lew rate $A_V = 1$ , $V_O = 2$ V to 8 $V_{PP}$                                                                          |                                      |            | 2.6    |            | V/µs    |  |

|                                      |                                 | , , 5                                                                                                                   | Falling (90% to 10%)                 |            | 1.6    |            |         |  |

<sup>(1)</sup> Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlations using Statistical Quality Control (SQC) method.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

<sup>(3)</sup> Positive current corresponds to current flowing into the device.

<sup>(4)</sup> The part is not short-circuit protected and is not recommended for operation with low resistive loads. Typical sourcing and sinking output current curves are provided in *Typical Characteristics* and should be consulted before designing for heavy loads.

# DC Electrical Characteristics: 10 V (continued)

Unless otherwise specified, all limits are specified for  $T_A = 25^{\circ}C$ ,  $V^+ = 10$  V,  $V^- = 0$  V,  $V_O = V_{CM} = V^+/2$ , and  $R_L > 1$  M $\Omega$ .

|                | PARAMETER                    | TEST CONDITIONS                                       | MIN<br>(1) | TYP    | MAX<br>(1) | UNIT               |

|----------------|------------------------------|-------------------------------------------------------|------------|--------|------------|--------------------|

| GBW            | Gain bandwidth product       |                                                       |            | 10     |            | MHz                |

| e <sub>n</sub> | Input-referred voltage noise | f = 1 kHz                                             |            | 14     |            | nV/√ <del>Hz</del> |

| i <sub>n</sub> | Input-referred current noise | f = 1 kHz                                             |            | 0.15   |            | pA/√ <del>Hz</del> |

| THD            | Total harmonic distortion    | $f = 1 \text{ kHz}, A_V = 2, R_L = 2 \text{ k}\Omega$ |            | 0.002% |            |                    |

Product Folder Links: LMV641

# TEXAS INSTRUMENTS

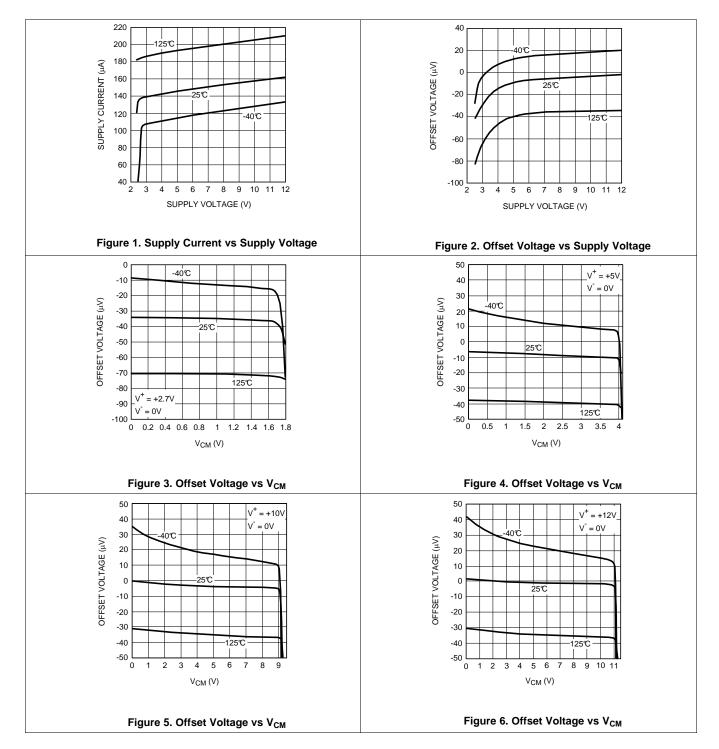

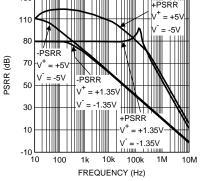

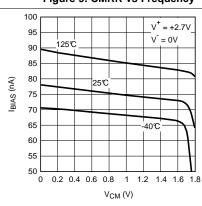

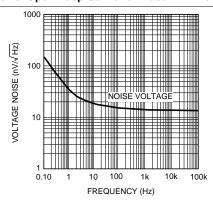

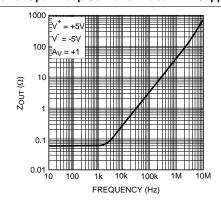

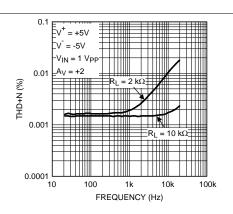

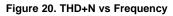

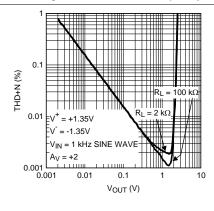

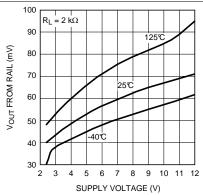

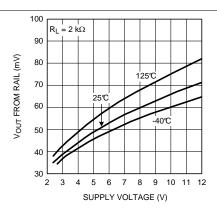

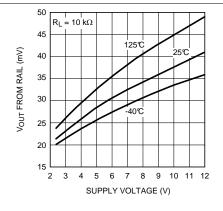

## 6.7 Typical Characteristics

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 10 \text{ V}$ ,  $V^- = 0 \text{ V}$ ,  $V_{CM} = V_S/2$ .

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

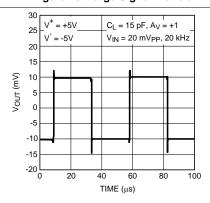

V<sup>+</sup> = +5V

V = -5V

V<sub>CM</sub> = 0V

T<sub>A</sub> = 25℃

## **Typical Characteristics (continued)**

0

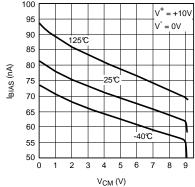

Figure 11. Input Bias Current vs V<sub>CM</sub>

Figure 12. Input Bias Current vs V<sub>CM</sub>

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

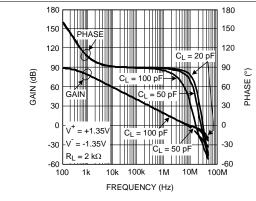

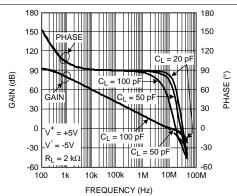

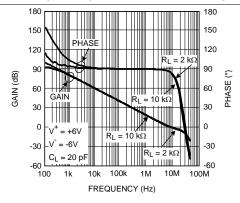

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 10 \text{ V}$ ,  $V^- = 0 \text{ V}$ ,  $V_{CM} = V_S/2$ .

Figure 13. Open-Loop Gain and Phase With Capacitive Load

Figure 14. Open-Loop Gain and Phase With Capacitive Load

Figure 15. Open-Loop Gain and Phase With Resistive Load

Figure 16. Open-Loop Gain and Phase With Supply Voltage

Figure 17. Input Referred Noise Voltage vs Frequency

Figure 18. Close Loop Output Impedance vs Frequency

## **Typical Characteristics (continued)**

Unless otherwise specified,  $T_A = 25$ °C,  $V^+ = 10$  V,  $V^- = 0$  V,  $V_{CM} = V_S/2$ .

Figure 19. THD+N vs Frequency

Figure 21. THD+N vs  $V_{\rm OUT}$

Figure 22. THD+N vs  $V_{\rm OUT}$

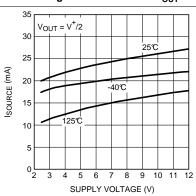

Figure 23. Sourcing Current vs Supply Voltage

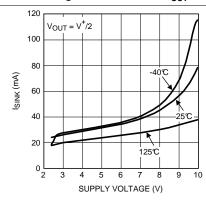

Figure 24. Sinking Current vs Supply Voltage

# TEXAS INSTRUMENTS

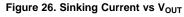

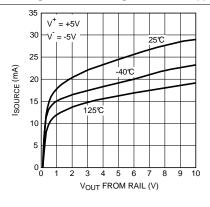

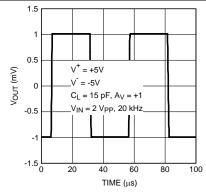

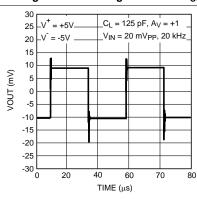

## **Typical Characteristics (continued)**

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 10 \text{ V}$ ,  $V^- = 0 \text{ V}$ ,  $V_{CM} = V_S/2$ .

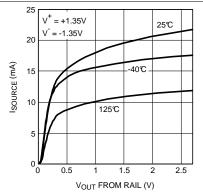

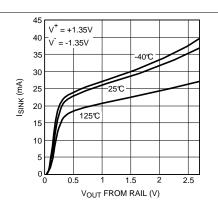

Figure 25. Sourcing Current vs  $V_{\text{OUT}}$

Figure 27. Sourcing Current vs  $V_{\text{OUT}}$

Figure 28. Large-Signal Transient

Figure 29. Small-Signal Transient Response

Figure 30. Small-Signal Transient Response

## **Typical Characteristics (continued)**

Unless otherwise specified,  $T_A = 25$ °C,  $V^+ = 10$  V,  $V^- = 0$  V,  $V_{CM} = V_S/2$ .

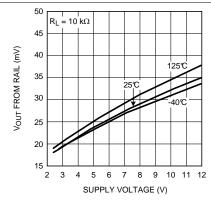

Figure 31. Output Swing High vs Supply Voltage

Figure 32. Output Swing Low vs Supply voltage

Figure 33. Output Swing High vs Supply Voltage

Figure 34. Output Swing Low and Supply Voltage

Figure 35. Slew Rate vs Supply Voltage

## 7 Detailed Description

#### 7.1 Overview

The LMV641 is a wide-bandwidth, low-power operational amplifier with an extended power supply voltage range of 2.7 V to 12 V. The device is unity-gain stable with a 10 MHz of gain bandwidth product. Operating on a typical supply current of 138  $\mu$ A, it provides a PSRR of 105 dB, CMRR of 120 dB, V<sub>OS</sub> of 500  $\mu$ V, input referred voltage noise of 14 nV/ $\sqrt{\text{Hz}}$ , and a THD of 0.002%. This amplifier has a rail-to-rail output stage and a common mode input voltage which includes the negative supply.

## 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 7.3 Feature Description

#### 7.3.1 Low-Voltage and Low-Power Operation

The LMV641 has performance guaranteed at supply voltages of 2.7 V and 10 V. It is ensured to be operational at all supply voltages between 2.7 V and 12 V. The LMV641 draws a low supply current of 138 µA. The LMV641 provides the low-voltage and low-power amplification, which is essential for portable applications.

#### 7.3.2 Wide Bandwidth

Despite drawing the very low supply current of 138 µA, the LMV641 manages to provide a wide unity gain bandwidth of 10 MHz. This is easily one of the best bandwidth to power ratios ever achieved, and allows this op amp to provide wideband amplification while using the minimum amount of power. This makes the LMV641 ideal for low power signal processing applications such as portable media players and other accessories.

#### 7.3.3 Low Input Referred Noise

The LMV641 provides a flatband input referred voltage noise density of 14 nV/Hz, which is significantly better than the noise performance expected from a low-power op amp. This op amp also feature exceptionally low 1/f noise, with a very low 1/f noise corner frequency of 4 Hz. Because of this the LMV641 is ideal for low-power applications which require decent noise performance, such as PDAs and portable sensors.

#### 7.3.4 Ground Sensing and Rail-to-Rail Output

The LMV641 has a rail-to-rail output stage, which provides the maximum possible output dynamic range. This is especially important for applications requiring a large output swing. The input common mode range of this part includes the negative supply rail which allows direct sensing at ground in a single supply operation.

#### 7.3.5 Small Size

The small footprint of the packages for the LMV641 saves space on printed-circuit boards, and enables the design of smaller and more compact electronic products. Long traces between the signal source and the op amp make the signal path susceptible to noise. By using a physically smaller package, these op amps can be placed closer to the signal source, reducing noise pickup and enhancing signal integrity.

Product Folder Links: LMV641

#### 7.4 Device Functional Modes

#### 7.4.1 Stability of Op Amp Circuits

If the phase margin of the LMV641 is plotted with respect to the capacitive load ( $C_L$ ) at its output, and if  $C_L$  is increased beyond 100 pF then the phase margin reduces significantly. This is because the op amp is designed to provide the maximum bandwidth possible for a low supply current. Stabilizing the LMV641 for higher capacitive loads would have required either a drastic increase in supply current, or a large internal compensation capacitance, which would have reduced the bandwidth. Hence, if this device is to be used for driving higher capacitive loads, it will have to be externally compensated.

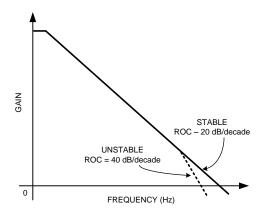

Figure 36. Gain vs Frequency for an Op Amp

An op amp, ideally, has a dominant pole close to DC which causes its gain to decay at the rate of 20 dB/decade with respect to frequency. If this rate of decay, also known as the rate of closure (ROC), remains the same until the op amp's unity gain bandwidth, then the op amp is stable. If, however, a large capacitance is added to the output of the op amp, it combines with the output impedance of the op amp to create another pole in its frequency response before its unity gain frequency (Figure 36). This increases the ROC to 40 dB/decade and causes instability.

In such a case, a number of techniques can be used to restore stability to the circuit. The idea behind all these schemes is to modify the frequency response such that it can be restored to an ROC of 20 dB/decade, which ensures stability.

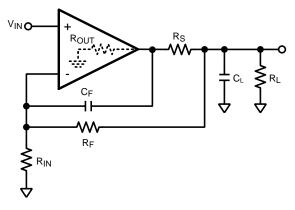

#### 7.4.1.1 In The Loop Compensation

Figure 37 illustrates a compensation technique, known as *in the loop* compensation, that employs an RC feedback circuit within the feedback loop to stabilize a non-inverting amplifier configuration. A small series resistance,  $R_S$ , is used to isolate the amplifier output from the load capacitance,  $C_L$ , and a small capacitance,  $C_F$ , is inserted across the feedback resistor to bypass  $C_L$  at higher frequencies.

Figure 37. In the Loop Compensation

## **Device Functional Modes (continued)**

The values for  $R_S$  and  $C_F$  are decided by ensuring that the zero attributed to  $C_F$  lies at the same frequency as the pole attributed to  $C_L$ . This ensures that the effect of the second pole on the transfer function is compensated for by the presence of the zero, and that the ROC is maintained at 20 dB/ decade. For the circuit shown in Figure 37 the values of  $R_S$  and  $C_F$  are given by Equation 1. Values of  $R_S$  and  $C_F$  required for maintaining stability for different values of  $C_L$ , as well as the phase margins obtained, are shown in Table 1.  $R_F$  and  $R_{IN}$  are 10 k $\Omega$ ,  $R_L$  is 2 k $\Omega$ , while  $R_{OUT}$  is 680 $\Omega$ .

$$R_{S} = \frac{R_{OUT}R_{IN}}{R_{F}}$$

$$C_{F} = \left(\frac{R_{F} + 2R_{IN}}{R_{F}^{2}}\right)C_{L}R_{OUT}$$

(1)

**Table 1. Loop Compensation Stability**

| C <sub>L</sub> (nF) | $R_S\left(\Omega\right)$ | C <sub>F</sub> (pF) | PHASE MARGIN (°) |

|---------------------|--------------------------|---------------------|------------------|

| 0.5                 | 680                      | 10                  | 17.4             |

| 1                   | 680                      | 20                  | 12.4             |

| 1.5                 | 680                      | 30                  | 10.1             |

The LMV641 is capable of driving heavy capacitive loads of up to 1 nF without oscillating, however it is recommended to use compensation should the load exceed 1 nF. Using this methodology will reduce any excessive ringing and help maintain the phase margin for stability. The values of the compensation network tabulated above illustrate the phase margin degradation as a function of the capacitive load.

Although this methodology provides circuit stability for any load capacitance, it does so at the price of bandwidth. The closed loop bandwidth of the circuit is now limited by  $R_F$  and  $C_F$ .

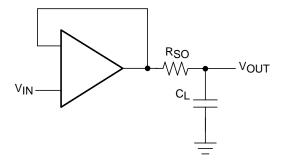

#### 7.4.1.2 Compensation by External Resistor

In some applications it is essential to drive a capacitive load without sacrificing bandwidth. In such a case, in the loop compensation is not viable. A simpler scheme for compensation is shown in Figure 38. A resistor,  $R_{\rm ISO}$ , is placed in series between the load capacitance and the output. This introduces a zero in the circuit transfer function, which counteracts the effect of the pole formed by the load capacitance, and ensures stability. The value of  $R_{\rm ISO}$  to be used should be decided depending on the size of  $C_L$  and the level of performance desired. Values ranging from  $5\Omega$  to  $50\Omega$  are usually sufficient to ensure stability. A larger value of  $R_{\rm ISO}$  will result in a system with less ringing and overshoot, but will also limit the output swing and the short circuit current of the circuit.

Figure 38. Compensation by Isolation Resistor

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LMV641 is a low-power, low noise, wide-bandwidth operational amplifier with an extended power supply voltage range of 2.7 V to 12 V. With 10 MHz of gain bandwidth, 14 nV/ $\sqrt{\text{Hz}}$  input referred noise, and supply current of 138  $\mu$ A, the LMV641 is well suited for portable applications that require precision while amplifying at high gains.

#### 8.2 Typical Applications

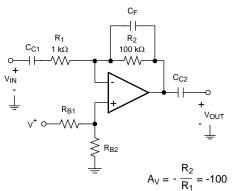

#### 8.2.1 High-Gain, Low-Power Inverting Amplifiers

Copyright © 2016, Texas Instruments Incorporated

Figure 39. High-Gain Inverting Amplifier

#### 8.2.1.1 Design Requirements

The wide unity-gain bandwidth allows these parts to provide large gain over a wide frequency range, while driving loads as low as 2  $k\Omega$  with less than 0.003% distortion.

#### 8.2.1.2 Detailed Design Procedure

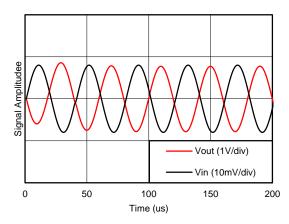

Figure 39 is an inverting amplifier, with a 100-k $\Omega$  feedback resistor, R<sub>2</sub>, and a 1-k $\Omega$  input resistor, R<sub>1</sub>, and provides a gain of –100. With the LMV641, these circuits can provide gain of –100 with a –3-dB bandwidth of 120 kHz, for a quiescent current as low as 116 μA. Coupling capacitors C<sub>C1</sub> and C<sub>C2</sub> can be added to isolate the circuit from DC voltages, while R<sub>B1</sub> and R<sub>B2</sub> provide DC biasing. A feedback capacitor C<sub>F</sub> can also be added to improve compensation.

#### 8.2.1.3 Application Curve

Figure 40. High Gain Inverting Amplifier Results

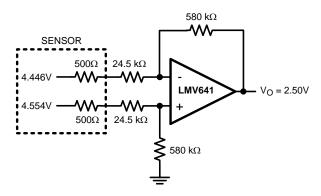

#### 8.2.2 Anisotropic Magnetoresistive Sensor

Copyright © 2016, Texas Instruments Incorporated

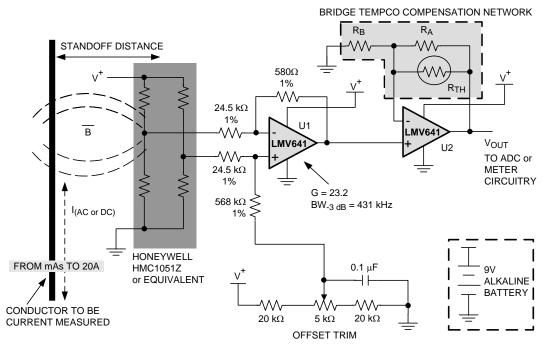

Figure 41. A Battery-Operated System for Contact-Less Current Sensing Using an Anisotropic Magnetoresistive Sensor

#### 8.2.2.1 Design Requirements

The low operating current of the LMV641 makes it a good choice for battery-operated applications. Figure 41 shows two LMV641s in a portable application with a magnetic field sensor. The LMV641s condition the output from an anisotropic magnetoresistive (AMR) sensor. The sensor is arranged in the form of a Wheatstone bridge. This type of sensor can be used to accurately measure the current (either DC or AC) flowing in a wire by measuring the magnetic flux density, **B**, emanating from the wire.

#### 8.2.2.2 Detailed Design Procedure

In this circuit, the use of a 9-V alkaline battery exploits the LMV641's high voltage and low supply current for a low-power, portable-current-sensing application. The sensor converts an incident magnetic field (through the magnetic flux linkage) in the sensitive direction, to a balanced voltage output. The LMV641 can be used for moderate to high current sensing applications (from a few milliamps and up to 20 A) using a nearby external conductor providing the sensed magnetic field to the bridge. The circuit shows a Honeywell HMC1051Z used as a current sensor. Note that the circuit must be calibrated based on the final displacement of the sensed conductor relative to the measurement bridge. Typically, once the sensor has been oriented properly, with respect to the conductor to be measured, the conductor can be placed about one centimeter away from the bridge and have reasonable capability of measuring from tens of milliamperes to beyond 20 amperes.

In Figure 41, U1 is configured as a single differential input amplifier. Its input impedance is relatively low, however, and requires that the source impedance of the sensor be considered in the gain calculations. Also, the asymmetrical loading on the bridge will produce a small offset voltage that can be cancelled out with the offset trim circuit shown in Figure 41.

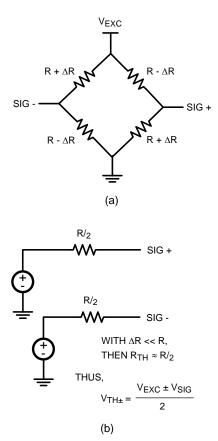

Figure 42 shows a typical magnetoresistive Wheatstone bridge and the Thevenin equivalent of its resistive elements. As we shall see, the Thevenin equivalent model of the sensor is useful in calculating the gain needed in the differential amplifier.

Figure 42. Anisotropic Magnetoresistive Wheatstone Bridge Sensor, (a), and Thevenin Equivalent Circuit, (b)

Using Thevenin's Theorem, the bridge can be reduced to two voltage sources with series resistances.  $\Delta R$  is normally very small in comparison to R, thus the Thevenin equivalent resistance, commonly called the source resistance, can be taken to be R. When a bias voltage is applied between  $V_{EXC}$  and ground, in the absence of a magnetic field, all of the resistances are considered equal. The voltage at Sig+ and Sig- is half  $V_{EXC}$ , or 4.5 V, and Sig+ - Sig- = 0. Bridges are designed such that, when immersed in a magnetic field, opposite resistances in the bridge change by  $\pm \Delta R$  with an amount proportional to the strength of the magnetic field. This causes the bridge's output differential voltage, to change from its half  $V_{EXC}$  value. Thus Sig+ - Sig- = Vsig  $\neq$  0. With four active elements, the output voltage is:

$$V_{SIG} = V_{EXC} x \frac{\Delta R}{R}$$

(2)

Because  $\Delta R$  is proportional to the field strength,  $B_S$ , the amount of output voltage from the sensor is a function of sensor sensitivity, S. This expression can rewritten as , where

$$V_{SIG} = V_{EXC} \cdot S \cdot B_{S}$$

#### where

- S = material constant (nominally 1 mV/V/gauss)

- B<sub>S</sub> = magnetic flux in gauss (3)

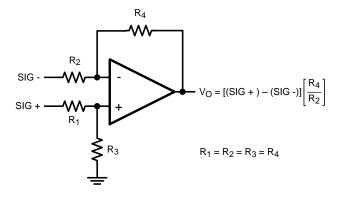

A simplified schematic of a single op amp, differential amplifier is shown in Figure 43. The Thevenin equivalent circuit of the sensor can be used to calculate the gain of this amplifier.

Figure 43. Differential Input Amplifier

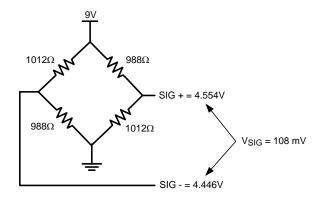

The Honeywell HMC1051Z AMR sensor has nominal 1-k $\Omega$  elements and a sensitivity of 1 mV/V/gauss and is being used with 9 V of excitation with a full scale magnetic field range of ±6 gauss. At full-scale, the resistors will have  $\Delta R \approx 12 \Omega$  and 108 mV will be seen from Sig- to Sig+ (see Figure 44).

Figure 44. Sensor Output with No Load

20

Referring to the simplified diagram in Figure 43, and assuming that required full scale at the output of the amplifier is 2.5 V, a gain of 23.2 is needed for U1. It is clear from the Thevenin equivalent circuit in Figure 45 that a sensor Thevenin equivalent source resistance,  $R_{THEV}$ , of 500  $\Omega$  will be in series with both the inverting and noninverting inputs of the LMV641. Therefore, the required gain is:

$$A_{VCL} = \frac{R_4}{R_{THEV} + R_2} = 23.2 \tag{4}$$

Choosing  $R_1 = R_2 = 24.5 \text{ k}\Omega$ , then  $R_4$  will be approximately 580 k $\Omega$ . The actual values chosen will depend on the full-scale needs of the succeeding circuitry as well as bandwidth requirements. The values shown here provide a -3-dB bandwidth of approximately 431 kHz, and are found as follows.

$$BW_{-3 dB} = \frac{GAIN-BANDWIDTH PRODUCT}{A_{VCL}} = \frac{10 \text{ MHz}}{23.2} = 431 \text{ kHz}$$

Figure 45. Thevenin Equivalent Showing Required Gain

By choosing input resistor values for  $R_1$  and  $R_2$  that are four to ten times the bridge element resistance, the bridge is minimally loaded and the offset errors induced by the op amp stages are minimized. These resistors should have 1% tolerance, or better, for the best noise rejection and offset minimization.

Referring once again to Figure 41, U2 is an additional gain stage with a thermistor element,  $R_{TH}$ , in the feedback loop. It performs a temperature compensation function for the bridge so that it will have greater accuracy over a wide range of operational temperatures. With mangetoresistive sensors, temperature drift of the bridge sensitivity is negative and linear, and in the case of the sensor used here, is nominally -3000 PP/M. Thus the gain of U2 needs to increase proportionally with increasing temperature, suggesting a thermistor with a positive temperature coefficient. Selection of the temperature compensation resistor,  $R_{TH}$ , depends on the additional gain required, on the thermistor chosen, and is dependent on the thermistor's %/°C shift in resistance. For best op amp compatibility, the thermistor resistance should be greater than 1000  $\Omega$ .  $R_{TH}$  should also be much less than  $R_A$ , the feedback resistor. Because the temperature coefficient of the AMR bridge is largely linear,  $R_{TH}$  also needs to behave in a linear fashion with temperature, thus  $R_A$  is placed in parallel with  $R_{TH}$ , which acts to linearize the thermistor.

#### 8.2.2.2.1 Gain Error and Bandwidth Consideration if Using an Analog to Digital Converter

The bandwidth available from Figure 41 is dependent on the system closed loop gain required and the maximum gain-error allowed if driving an analog to digital converter (ADC). If the output from the sensor is intended to drive an ADC, the bandwidth will be considerably reduced from the closed-loop corner frequency. This is because the gain error of the pre-amplifier stage needs to be taken into account when calculating total error budget. Good practice dictates that the gain error of the amplifier be less than or equal to half LSB (preferably less in order to allow for other system errors that will eat up a portion of the available error budget) of the ADC. However, at the -3 dB corner frequency the gain error for any amplifier is 29.3%. In reality, the gain starts rolling off long before the -3 dB corner is reached. For example, if the amplifier is driving an 8-bit ADC, the minimum gain error allowed for half LSB would be approximately 0.2%. To achieve this gain error with the op amp, the maximum frequency of interest can be no higher than

Copyright © 2007–2016, Texas Instruments Incorporated

$$\sqrt{\frac{1}{\left(1 - \frac{1}{2^{n+1}}\right)^2}} - 1 \times f_{-3 \text{ dB}}$$

where

n is the bit resolution of the ADC

Given that the LMV641 has a GBW of 10 MHz, and is operating with a closed loop gain of 26.3, its closed loop bandwidth is 380 kHZ, therefore

MAX FREQ =

$$\sqrt{\frac{1}{1 - \frac{1}{2^{n+1}}}} - 1 = 0.062 \text{ x f}_{-3 \text{ dB}}$$

$$= 0.062 \text{ x } 380 \text{ kHz} = 23.56 \text{ kHz}$$

(6)

which is the highest frequency that can be measured with required accuracy.

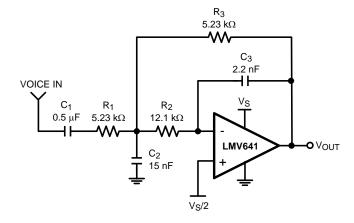

#### 8.2.3 Voiceband Filter

The majority of the energy of recognizable speech is within a band of frequencies between 200 Hz and 4 kHz. Therefore, it is beneficial to design circuits which transmit telephone signals that pass only certain frequencies and eliminate unwanted signals (noise) that could interfere with conversations and introduce error into control signals. The pass band of these circuits is defined as the ranges of frequencies that are passed. A telephone system voice frequency (VF) channel has a pass band of 0 Hz to 4 kHz. Specifically for human voices most of the energy content is found from 300 Hz to 3 kHz and any signal within this range is considered an in-band signal. Alternatively, any signal outside this range but within the VF channel is considered an out-of-band signal.

To properly recover a voice signal in applications such as cellular phones, cordless phones, and voice pagers, a low power bandpass filter that is matched to the human voice spectrum can be implemented using an LMV641 op amp. Figure 46 shows a multi-feedback, multi-pole filter ( $2^{nd}$  order response) with a gain of  $\neg 1$ . The lower 3 dB cutoff frequency which is set by the DC blocking capacitor  $C_1$  and resistor  $R_1$  is 60 Hz and the upper cutoff frequency is 3.5 kHz.

The total current consumption is a mere 138  $\mu$ A. The LV641 is operating with a gain of -1, but the circuit is easily modified to add gain. The op amp is powered from a single supply, hence the need for offset (common-mode) adjustment of its output, which is set to  $\frac{1}{2}$  V<sub>S</sub> via its non-inverting input.

This filter is also useful in applications for battery operated talking toys and games.

Figure 46. Low Power Voice In-Band Receive Filter for Battery-Powered Portable Use

22

## 9 Power Supply Recommendations

For proper operation, the power supplies must be properly decoupled. For decoupling the supply lines, TI recommends that 10-nF capacitors be placed as close as possible to the op amp power supply pins. For single supply, place a capacitor between V+ and V- supply leads. For dual supplies, place one capacitor between V+ and ground, and one capacitor between V- and ground.

## 10 Layout

## 10.1 Layout Guidelines

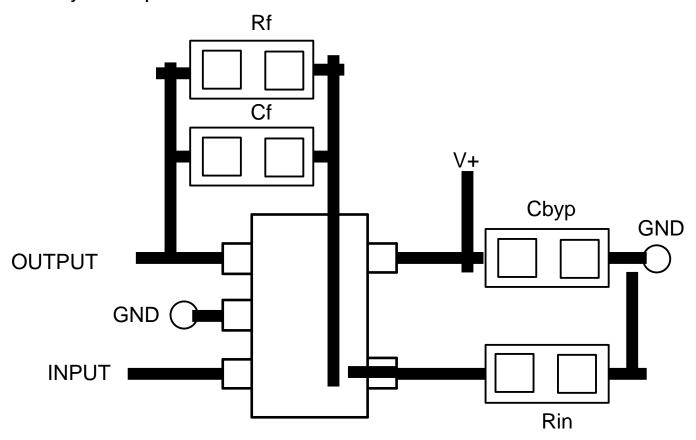

To properly bypass the power supply, several locations on a printed circuit board need to be considered. A 6.8  $\mu$ F or greater tantalum capacitor should be placed at the point where the power supply for the amplifier is introduced onto the board. Another 0.1- $\mu$ F ceramic capacitor should be placed as close as possible to the power supply pin of the amplifier. If the amplifier is operated in a single power supply, only the V+ pin needs to be bypassed with a 0.1- $\mu$ F capacitor. If the amplifier is operated in a dual power supply, both V+ and V- pins need to be bypassed. It is good practice to use a ground plane on a printed-circuit board to provide all components with a low-inductive ground connection.

#### 10.2 Layout Example

Figure 47. LMV641 Layout Example

Copyright © 2007–2016, Texas Instruments Incorporated

## 11 Device and Documentation Support

## 11.1 Device Support

#### 11.1.1 Development Support

For development support see the following:

- LMV641 PSPICE Model

- TINA-TI SPICE-Based Analog Simulation Program

- DIP Adapter Evaluation Module

- TI Universal Operational Amplifier Evaluation Module

- TI Filterpro Software

#### 11.2 Documentation Support

## 11.2.1 Related Documentation

For related documentation see the following:

- Absolute Maximum Ratings for Soldering (SNOA549)

- AN-29 IC Op Amp Beats FETs on Input Current (SNOA624)

- AN-31 Op Amp Circuit Collection (SNLA140)

- AN-71 Micropower Circuits Using the LM4250 Programmable Op Amp (SNOA652)

- AN-127 LM143 Monolithic High Voltage Operational Amplifier Applications (SNVA516)

## 11.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.4 Community Resource

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.5 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.6 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

Product Folder Links: LMV641

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: LMV641

4-Feb-2016

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing |   | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|---|----------------|----------------------------|------------------|--------------------|--------------|-------------------------|---------|

| LMV641MA/NOPB    | ACTIVE | SOIC         | D                  | 8 | 95             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | LMV64<br>1MA            | Samples |

| LMV641MAE/NOPB   | ACTIVE | SOIC         | D                  | 8 | 250            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | LMV64<br>1MA            | Samples |

| LMV641MAX/NOPB   | ACTIVE | SOIC         | D                  | 8 | 2500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | LMV64<br>1MA            | Samples |

| LMV641MF/NOPB    | ACTIVE | SOT-23       | DBV                | 5 | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |              | AB9A                    | Samples |

| LMV641MFE/NOPB   | ACTIVE | SOT-23       | DBV                | 5 | 250            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |              | AB9A                    | Samples |

| LMV641MFX/NOPB   | ACTIVE | SOT-23       | DBV                | 5 | 3000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |              | AB9A                    | Samples |

| LMV641MG/NOPB    | ACTIVE | SC70         | DCK                | 5 | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | A99                     | Samples |

| LMV641MGE/NOPB   | ACTIVE | SC70         | DCK                | 5 | 250            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | A99                     | Samples |

| LMV641MGX/NOPB   | ACTIVE | SC70         | DCK                | 5 | 3000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | A99                     | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

## **PACKAGE OPTION ADDENDUM**

4-Feb-2016

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

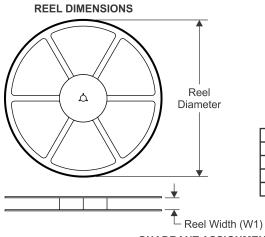

## PACKAGE MATERIALS INFORMATION

www.ti.com 4-Feb-2016

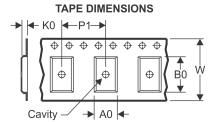

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

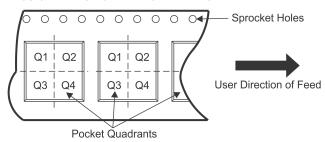

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMV641MAE/NOPB | SOIC            | D                  | 8 | 250  | 178.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LMV641MAX/NOPB | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LMV641MF/NOPB  | SOT-23          | DBV                | 5 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMV641MFE/NOPB | SOT-23          | DBV                | 5 | 250  | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMV641MFX/NOPB | SOT-23          | DBV                | 5 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMV641MG/NOPB  | SC70            | DCK                | 5 | 1000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LMV641MGE/NOPB | SC70            | DCK                | 5 | 250  | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LMV641MGX/NOPB | SC70            | DCK                | 5 | 3000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

www.ti.com 4-Feb-2016

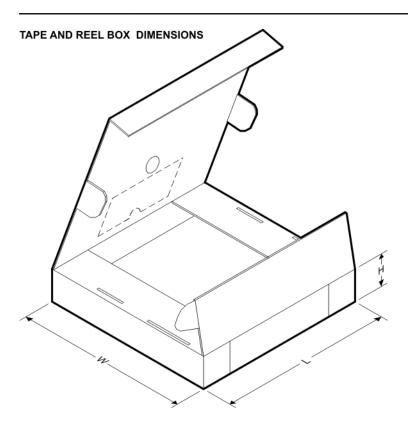

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMV641MAE/NOPB | SOIC         | D               | 8    | 250  | 210.0       | 185.0      | 35.0        |

| LMV641MAX/NOPB | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LMV641MF/NOPB  | SOT-23       | DBV             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LMV641MFE/NOPB | SOT-23       | DBV             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| LMV641MFX/NOPB | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LMV641MG/NOPB  | SC70         | DCK             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LMV641MGE/NOPB | SC70         | DCK             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| LMV641MGX/NOPB | SC70         | DCK             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

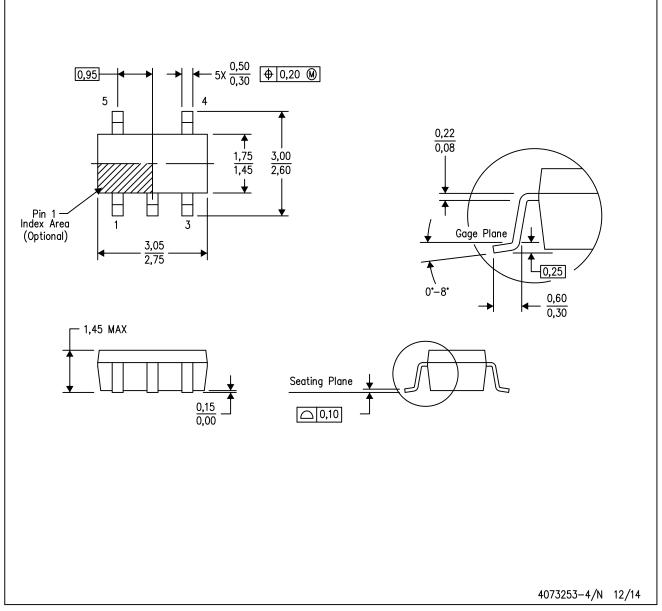

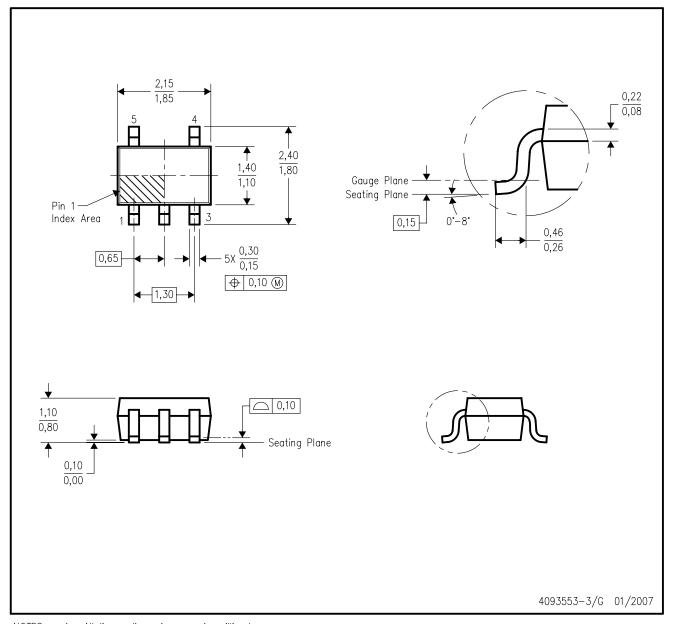

DBV (R-PDSO-G5)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-178 Variation AA.

# DCK (R-PDSO-G5)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-203 variation AA.

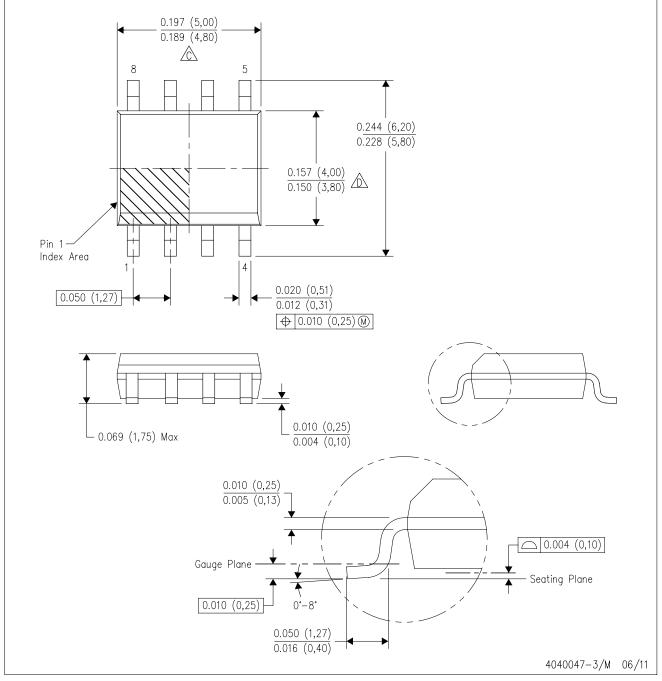

# D (R-PDSO-G8)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic Security www.ti.com/security logic.ti.com

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity